• You should create and download this example to the Intel Agilex SoC Development Kit.

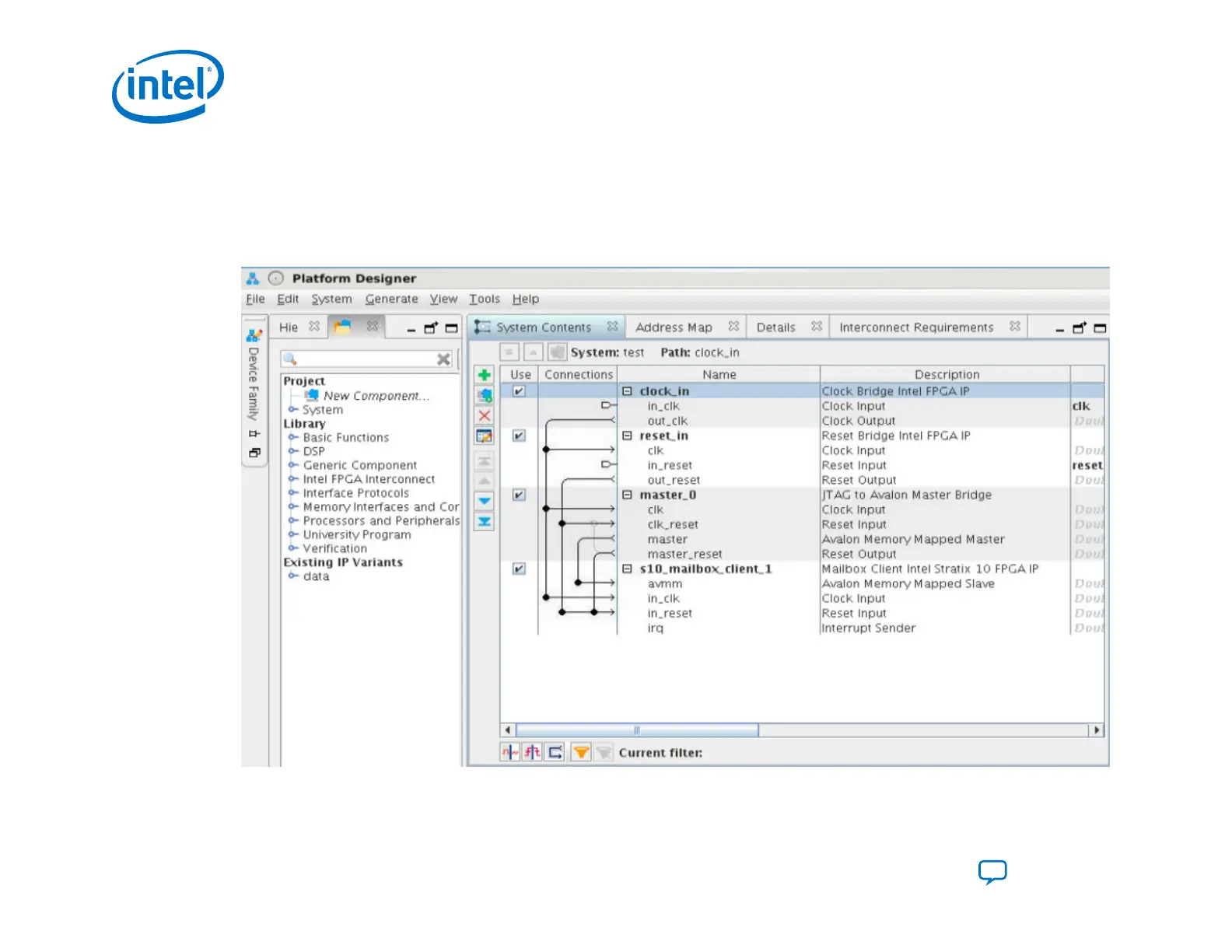

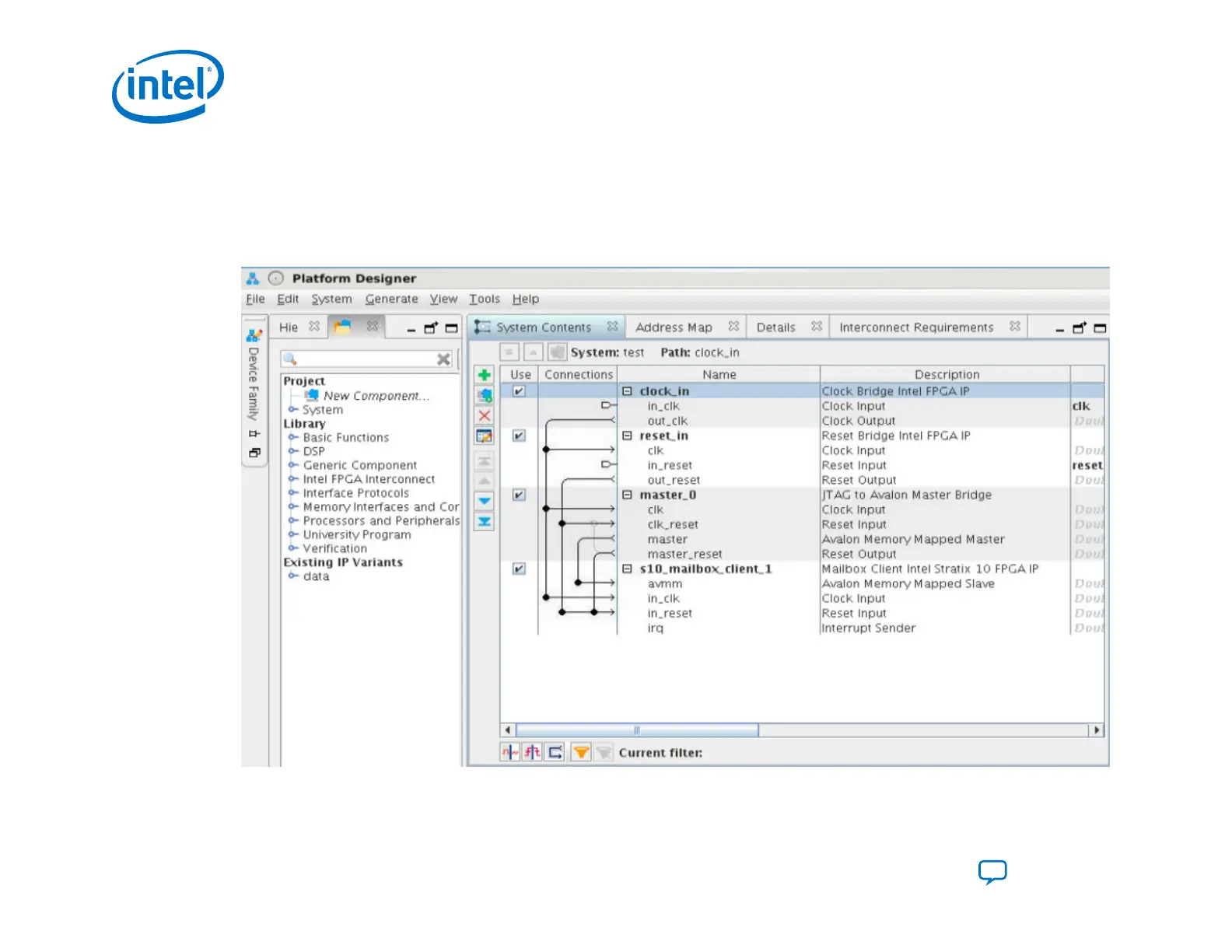

• Your design should include the Mailbox Client Intel FPGA IP that connects to a JTAG to Avalon Master Bridge as shown the

Platform Designer system. The JTAG to Avalon Master Bridge acts as the remote system update host controller for your

factory and application images.

Figure 67. Required Communication and Host Components for the Remote System Update Design Example

4. Remote System Update (RSU)

UG-20205 | 2019.10.09

Intel

®

Agilex

™

Configuration User Guide

Send Feedback

160

Loading...

Loading...