RL78/G13 CHAPTER 6 TIMER ARRAY UNIT

R01UH0146EJ0100 Rev.1.00 373

Sep 22, 2011

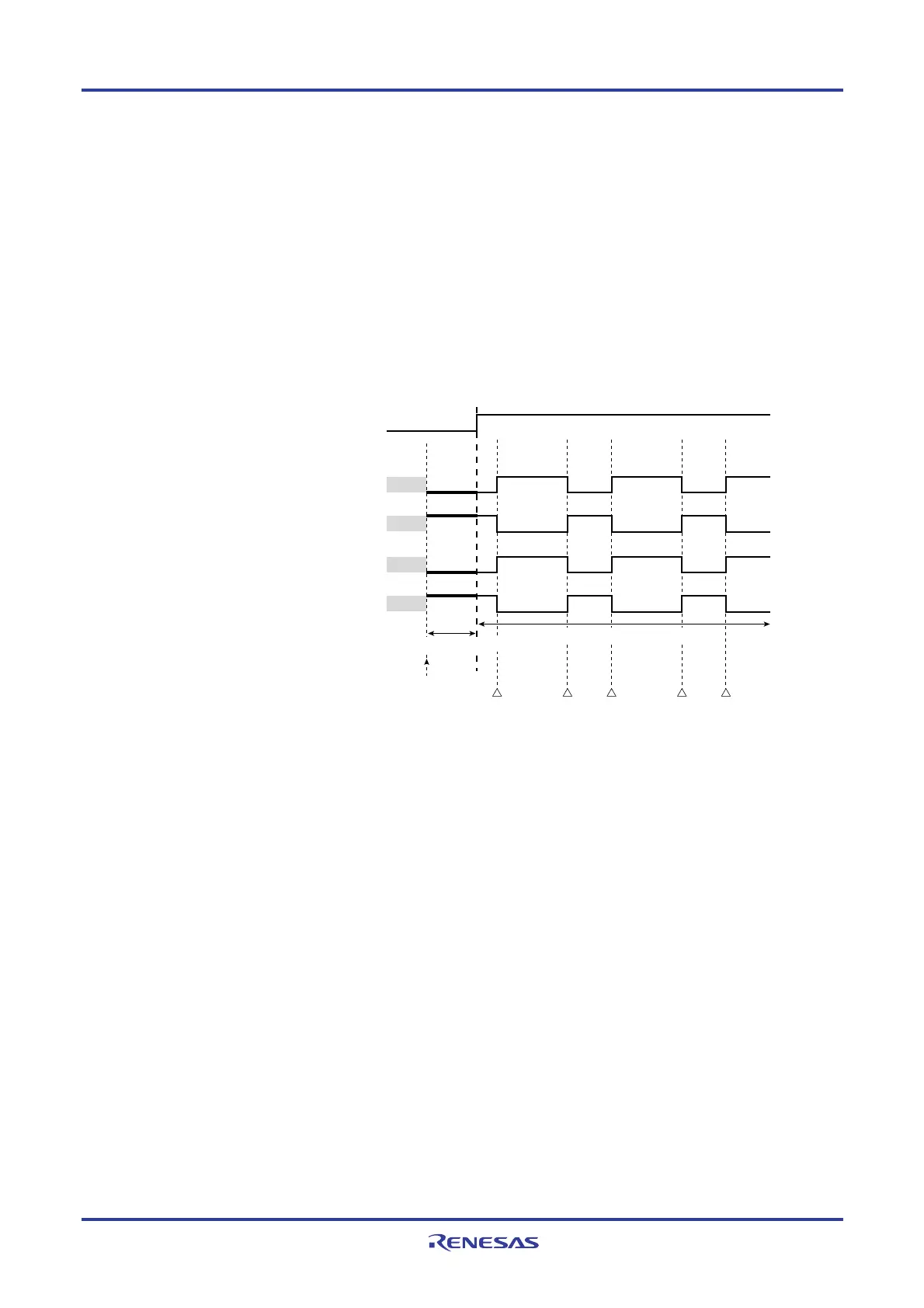

(2) Default level of TOmn pin and output level after timer operation start

The change in the output level of the TOmn pin when timer output register m (TOm) is written while timer output is

disabled (TOEmn = 0), the initial level is changed, and then timer output is enabled (TOEmn = 1) before port

output is enabled, is shown below.

(a) When operation starts with master channel output mode (TOMmn = 0) setting

The setting of timer output level register m (TOLm) is invalid when master channel output mode (TOMmn = 0).

When the timer operation starts after setting the default level, the toggle signal is generated and the output

level of the TOmn pin is reversed.

Figure 6-30. TOmn Pin Output Status at Toggle Output (TOMmn = 0)

TOEmn

TOmn = 0, TOLmn = 0

TOmn = 1, TOLmn = 0

TOmn = 0, TOLmn = 1

(Same output waveform as TOLmn = 0)

TOmn = 1, TOLmn = 1

(Same output waveform as TOLmn = 0)

Default level, TOLmn setting

Independent of TOLmn setting

Port output is enabled

TO0n pin transition

Toggle Toggle Toggle Toggle Toggle

Hi-Z

Hi-Z

Hi-Z

Hi-Z

Dependent on TOmn setting

Remarks 1. Toggle: Reverse TOmn pin output status

2. m: Unit number (m = 0, 1), n: Channel number (n = 0 to 7)

<R>

Loading...

Loading...