RL78/G13 CHAPTER 16 INTERRUPT FUNCTIONS

R01UH0146EJ0100 Rev.1.00 825

Sep 22, 2011

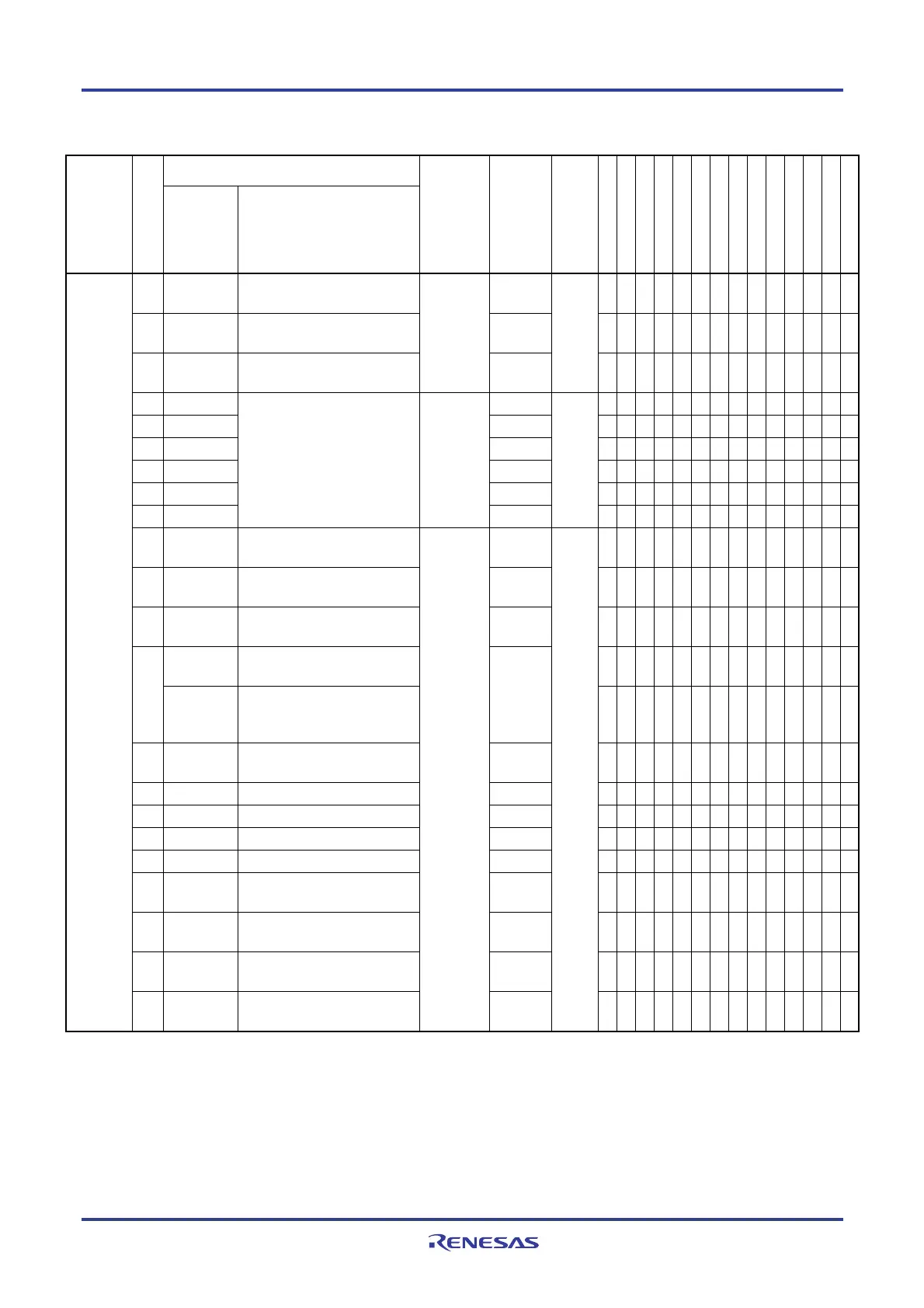

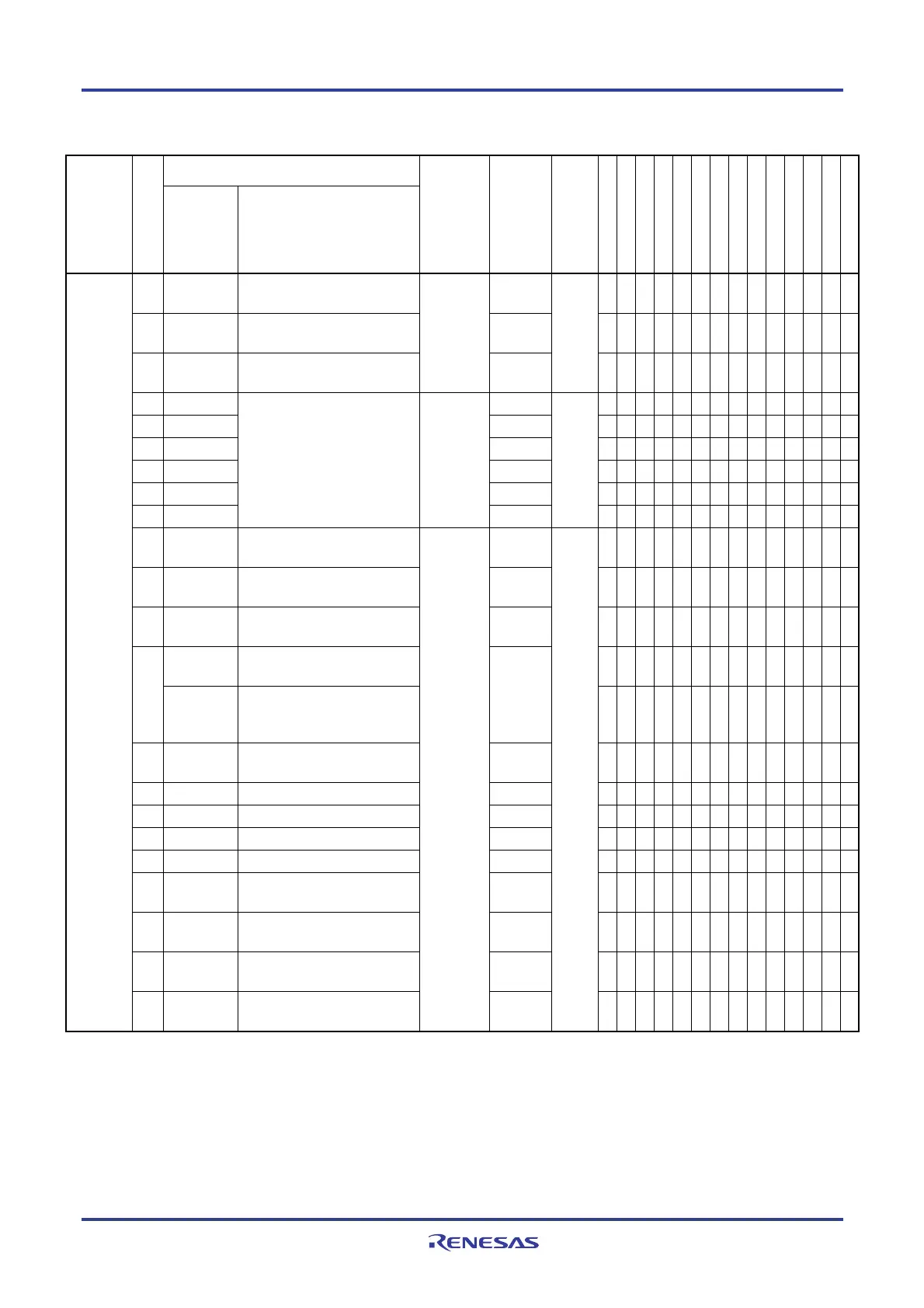

Table 16-1. Interrupt Source List (3/4)

Interrupt Source

Interrupt

Type

Default Priority

Note 1

Name Trigger

Internal/

External

Vector

Table

Address

Basic Configuration

Type

Note 2

128-pin

100-pin

80-pin

64-pin

52-pin

48-pin

44-pin

40-pin

36-pin

32-pin

30-pin

25-pin

24-pin

20-pin

32 INTTM05 End of timer channel 5 count

or capture

0044H √ √ √ √ √ √ √ √ √ √ √ √ √ √

33 INTTM06 End of timer channel 6 count

or capture

0046H √ √ √ √ √ √ √ √ √ √ √ √ √ √

34 INTTM07 End of timer channel 7 count

or capture

Internal

0048H

(A)

√ √ √ √ √ √ √ √ √ √ √ √ √ √

35 INTP6 004AH √ √ √ √ √ √ − − − − − − − −

36 INTP7 004CH √ √ √ √ − − − − − − − − − −

37 INTP8 004EH √ √ √ √ √ √ − − − − − − − −

38 INTP9 0050H √ √ √ √ √ √ − − − − − − − −

39 INTP10 0052H √ √ √ √ √ − − − − − − − − −

40 INTP11

Pin input edge detection External

0054H

(B)

√ √ √ √ √ − − − − − − − − −

41 INTTM10 End of timer channel 10 count

or capture

0056H √ √ √ − − − − − − − − − − −

42 INTTM11 End of timer channel 11 count

or capture

0058H √ √ √ − − − − − − − − − − −

43 INTTM12 End of timer channel 12 count

or capture

005AH √ √ √ − − − − − − − − − − −

INTSRE3

UART3 reception

communication error occurrence

√ √ √ − − − − − − − − − − −44

INTTM13H End of timer channel 13 count

or capture (at 8-bit timer

operation)

005CH

√ √ √ − − − − − − − − − − −

45 INTMD End of division operation/

Overflow occur

005EH √ √ √ √ √ √ √ √ √ √ √ √ √ √

46 INTIICA1 End of IICA1 communication 0060H √ √ √ − − − − − − − − − − −

47 INTFL End of sequencer interrupt

Note 3

0062H √ √ √ √ √ √ √ √ √ √ √ √ √ √

48 INTDMA2 End of DMA2 transfer 0064H √ √ √ − − − − − − − − − − −

49 INTDMA3 End of DMA3 transfer 0066H √ √ √ − − − − − − − − − − −

50 INTTM14 End of timer channel 14 count

or capture

0068H √ − − − − − − − − − − − − −

51 INTTM15 End of timer channel 15 count

or capture

006AH √ − − − − − − − − − − − − −

52 INTTM16 End of timer channel 16 count

or capture

006CH √ − − − − − − − − − − − − −

Maskable

53 INTTM17 End of timer channel 17 count

or capture

Internal

006EH

(A)

√ − − − − − − − − − − − − −

Notes 1. The default priority determines the sequence of interrupts if two or more maskable interrupts occur

simultaneously. Zero indicates the highest priority and 53 indicates the lowest priority.

2. Basic configuration types (A) to (D) correspond to (A) to (D) in Figure 16-1.

3. Be used only at the self programming library.

<R>

<R>

<R>

Loading...

Loading...