UM0306 USB full speed device interface (USB)

441/519

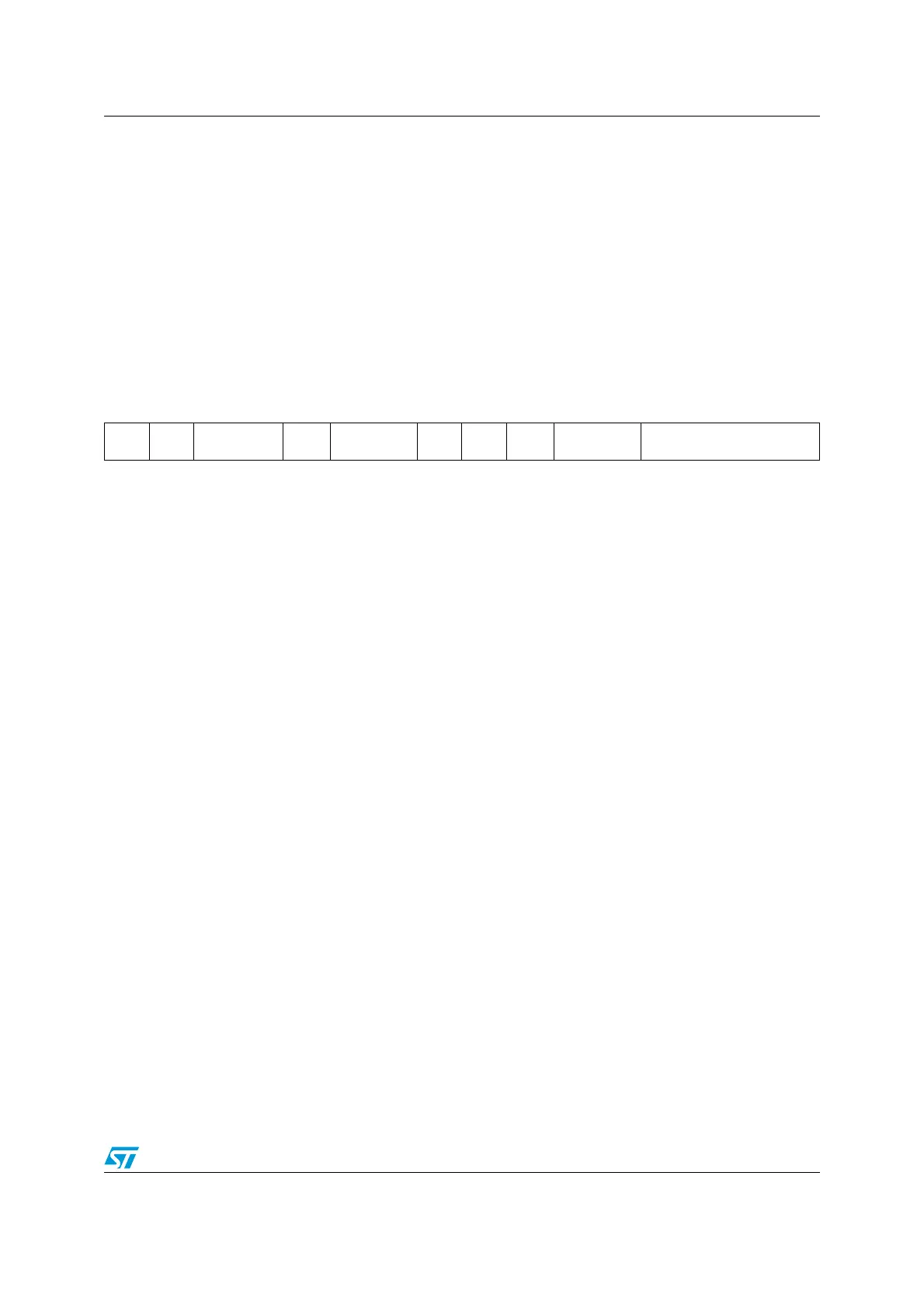

18.6.2 Endpoint-specific registers

The number of these registers varies according to the number of endpoints that the USB

Peripheral is designed to handle. The USB Peripheral supports up to 8 bidirectional

endpoints. Each USB device must support a control endpoint whose address (EA bits) must

be set to 0. The USB Peripheral behaves in an undefined way if multiple endpoints are

enabled having the same endpoint number value. For each endpoint, an register is

available to store the endpoint specific information.

USB endpoint n register (), n=[0..7]

Address Offset: 00h to 1Ch

Reset value: 0000 0000 0000 0000b (0000h)

They are also reset when an USB reset is received from the USB bus or forced through bit

FRES in the CTLR register, except the CTR_RX and CTR_TX bits, which are kept

unchanged to avoid missing a correct packet notification immediately followed by an USB

reset event. Each endpoint has its register where n is the endpoint identifier.

Read-modify-write cycles on these registers should be avoided because between the read

and the write operations some bits could be set by the hardware and the next write would

modify them before the CPU has the time to detect the change. For this purpose, all bits

affected by this problem have an ‘invariant’ value that must be used whenever their

modification is not required. It is recommended to modify these registers with a load

instruction where all the bits, which can be modified only by the hardware, are written with

their ‘invariant’ value.

1514131211109876543210

CTR_

RX

DTOG

_RX

STAT__X[1:0] SETUP

EP

TYPE[1:0]

EP_

KIND

CTR_

TX

DTOG_

TX

STAT_TX[1:0] EA[3:0]

r-c t t t r rwrwrwr-c t t t rwrwrwrw

Loading...

Loading...