Manual VIPA CPU 21x Chapter 12 Instruction list

HB103E - Rev. 05/45 12-9

Indirect addressing timer/counter

SP T [LW 8] Start timer; timer no. is in local data word 8.

CU C [LW 10] Start counter; counter no. is in local data word 10.

Memory-indirect, area-internal addressing

A I [LD 12]

e.g.: LP#22.2

T LD 12

A I [LD 12]

AND instruction; input address is in local data

double word 12 as pointer.

A I [DBD 1] AND instruction; input address is in data double

word 1 of the DB as pointer.

A Q [DID 12] AND instruction; output address is in data double

word 12 of the instance DB as pointer.

A Q [MD 12] AND instruction; output address is in bit memory

double word 12 as pointer.

Register-indirect, area-internal addressing

A I [AR1,P#12.2]

AND instruction; input address is calculated

"pointer value in address register 1 + pointer

P#12.2".

Register-indirect, area-crossing addressing

For the area-crossing, register indirect addressing the address needs an

additional range-ID in the Bits 24-26. The address is in the address

register.

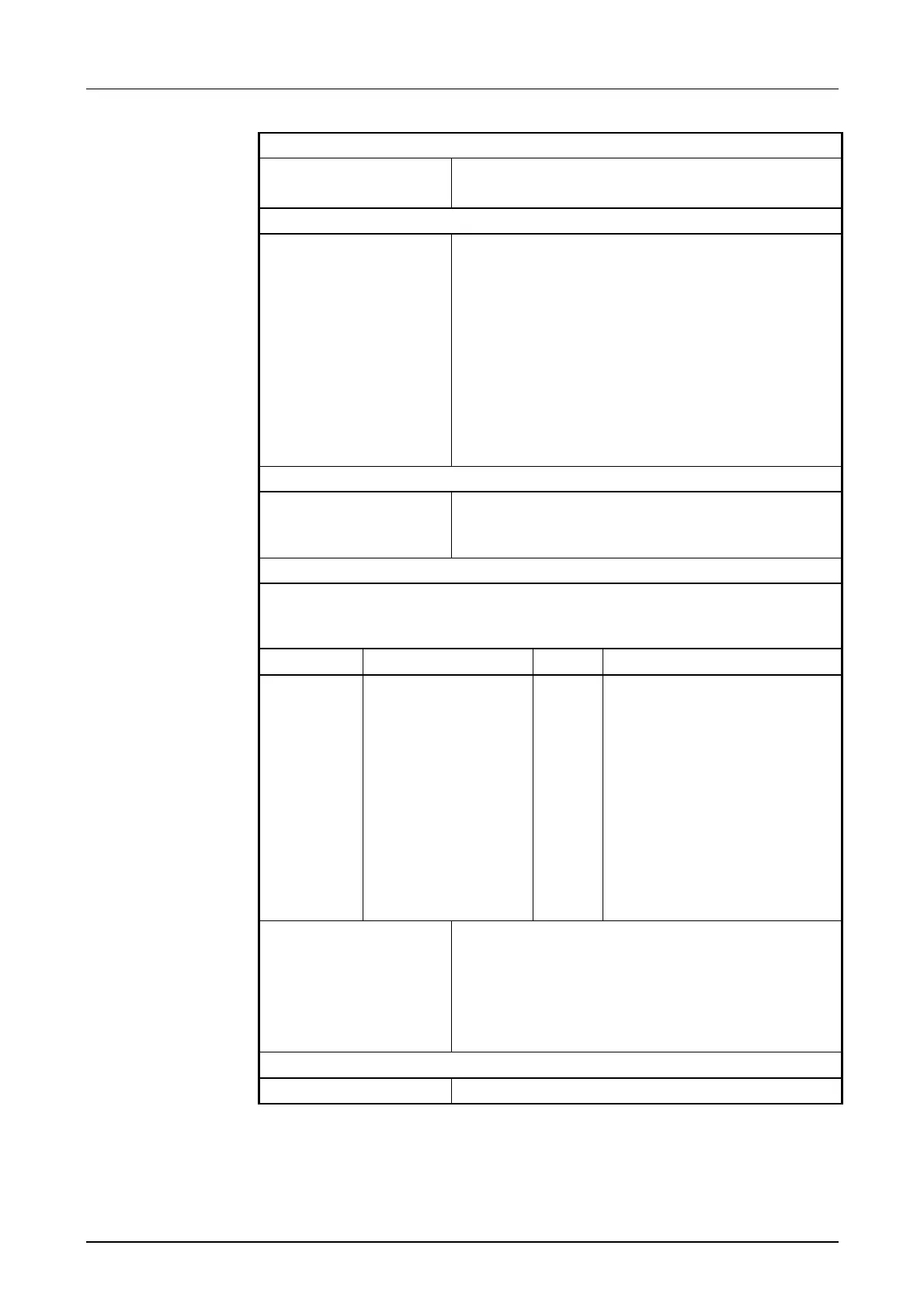

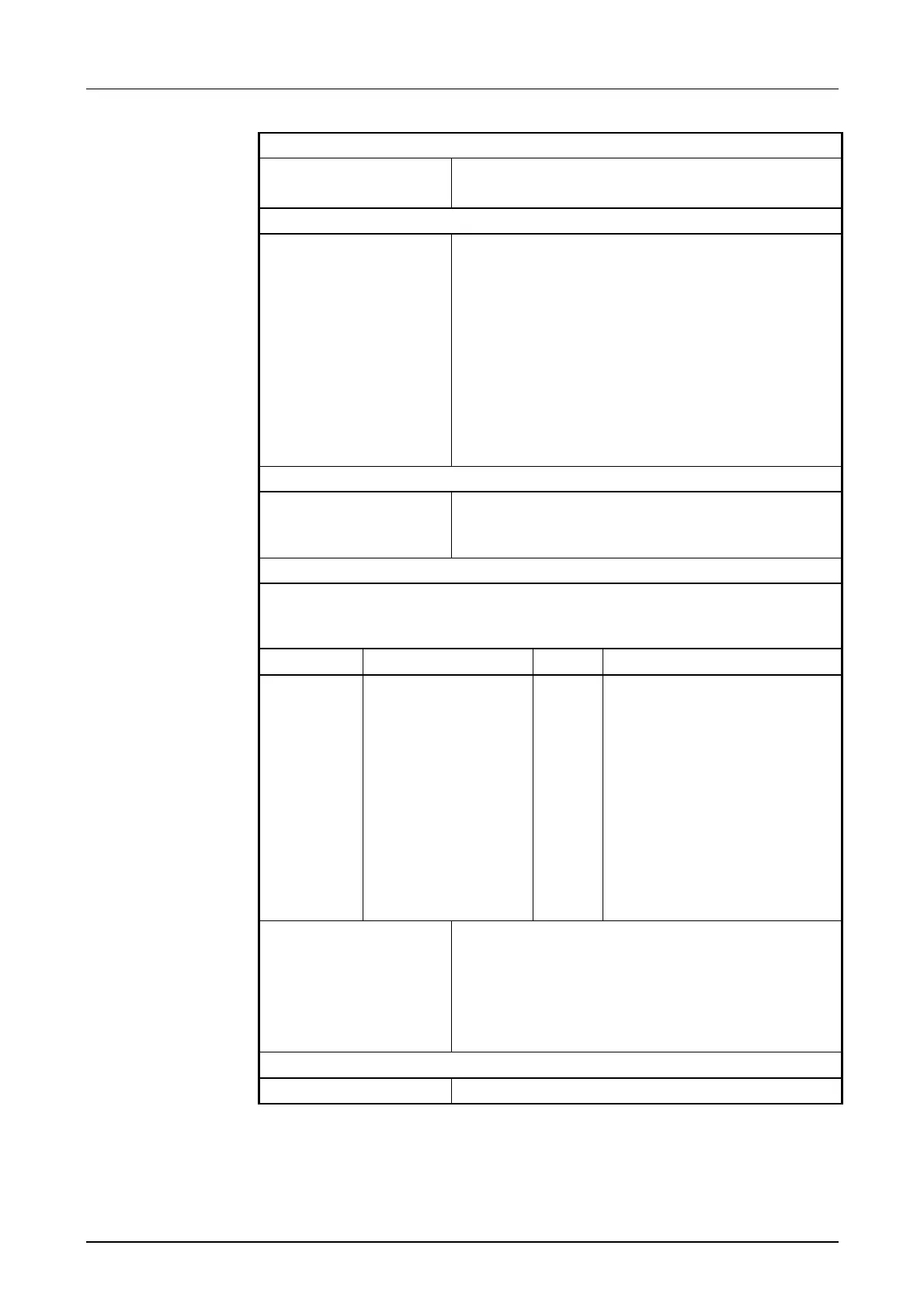

Range-ID Binary code hex. Area

P

1000 0000

80 Periphery area

I

1000 0001

81 Input area

Q

1000 0010

82 Output area

M

1000 0011

83 Bit memory area

DB

1000 0100

84 Data area

DI

1000 0101

85 Instance data area

L

1000 0110

86 Local data area

VL

1000 0111

87 Preceding local data area

(access to the local data of

the calling block)

L B [AR1,P#8.0]

Load byte in ACCU1; the address is calculated

"pointer value in address register 1

+ pointer P#8.0".

A [AR1,P#32.3]

AND instruction; operand address is calculated

"pointer value in address register 1

+ pointer P#32.3".

Addressing via parameters

A parameter The operand is addressed via the parameter.

Loading...

Loading...