Chapter 10 Deployment CPU 21xSER-2 Manual VIPA CPU 21x

10-2 HB103E - Rev. 05/45

Principles

The CPU 21x-2BS02 provide serial interfacing facilities between the

processes of different source and destination systems. The CPU has got 2

serial RS232C interfaces.

The communication happens via handling blocks that are stored in the

CPU as library.

The CPU 21x supports the ASCII, STX/ETX, 3964(R) and RK512

protocols.

For the parameter transfer to the communication processor (CP), you have

to execute SEND (SFC 230) with order no. 201 during runtime. For this you

store the parameters in a DB where the structure depends on the wanted

protocol.

To activate the parameters, you execute a RESET (SFC 234) with order

no. 0 after the SEND.

Note!

Please regard that the commands SEND, RECEIVE, FETCH and RESET

require a preceding "VKE"=1 otherwise they are not executed.

The internal CP of the CPU 21x-2BS02 is directly connected to the CPU

portion via a Dual-Port-RAM, also called "page frame". This page frame is

available at the CPU section as standard CP interface. The data transfer

happens via the standard handling blocks (SEND, RECEIVE and FETCH).

The communication via the according protocols is controlled by connection

commands that are programmed in the user application.

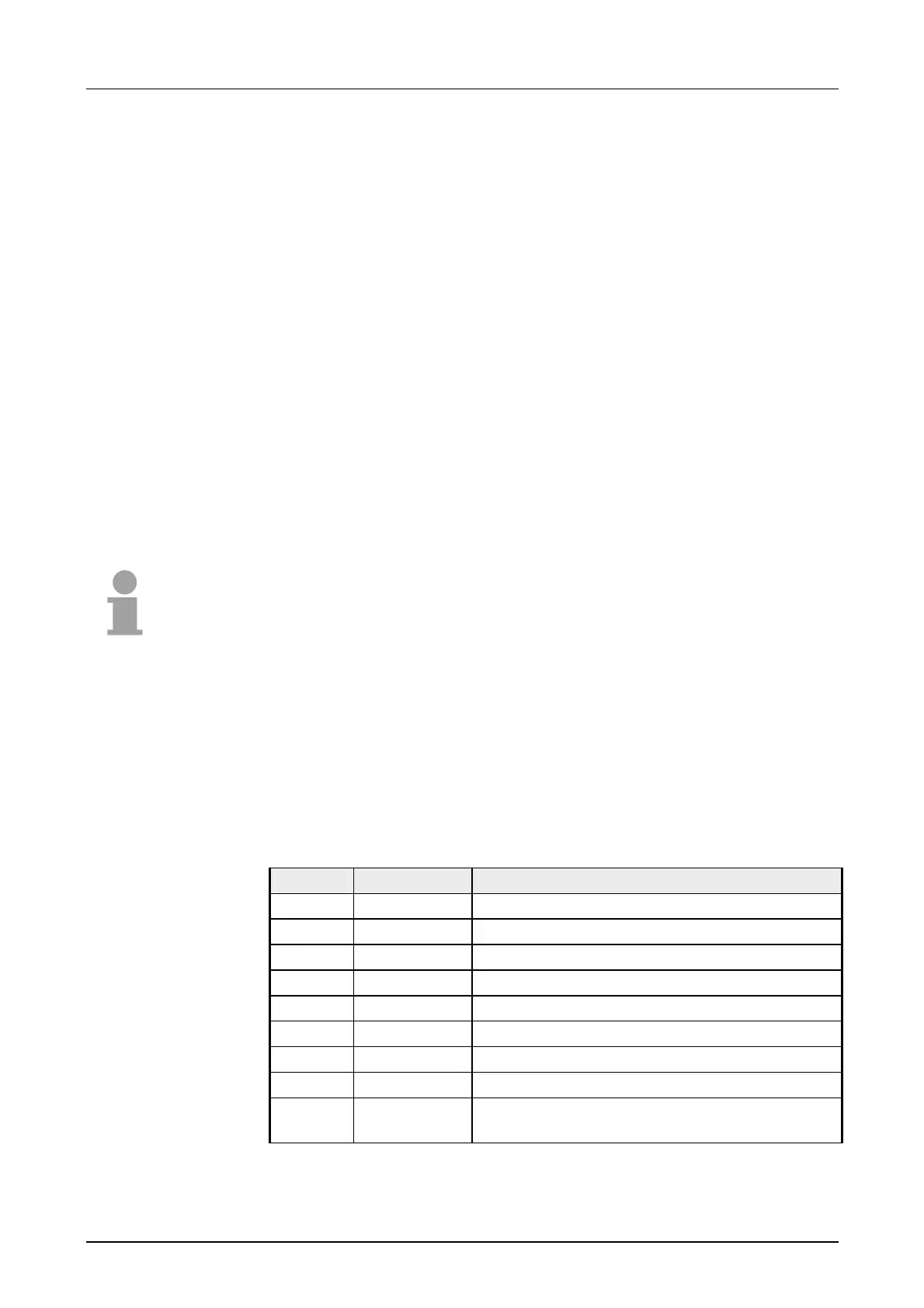

The following SFCs are deployed:

SFC Name Description

SFC 230 Send Send via page frame (page frame comm.)

SFC 231 Receive Receive via page frame (page frame comm.)

SFC 232 Fetch Fetch via page frame (page frame comm.)

SFC 233 Control Control for page frame communication

SFC 234 Reset Reset for page frame communication

SFC 235 Synchron Synchron for page frame communication

SFC 236 Send_All Send_All via page frame (page frame comm.)

SFC 237 Recv_All Receive_All via page frame (page frame com.)

SFC 238 Control1 Control for page frame communication

with Type ANZW: pointer and parameter IND.

General

Protocols

Parameterization

Communication

Loading...

Loading...