Manual VIPA CPU 21x Chapter 12 Instruction list

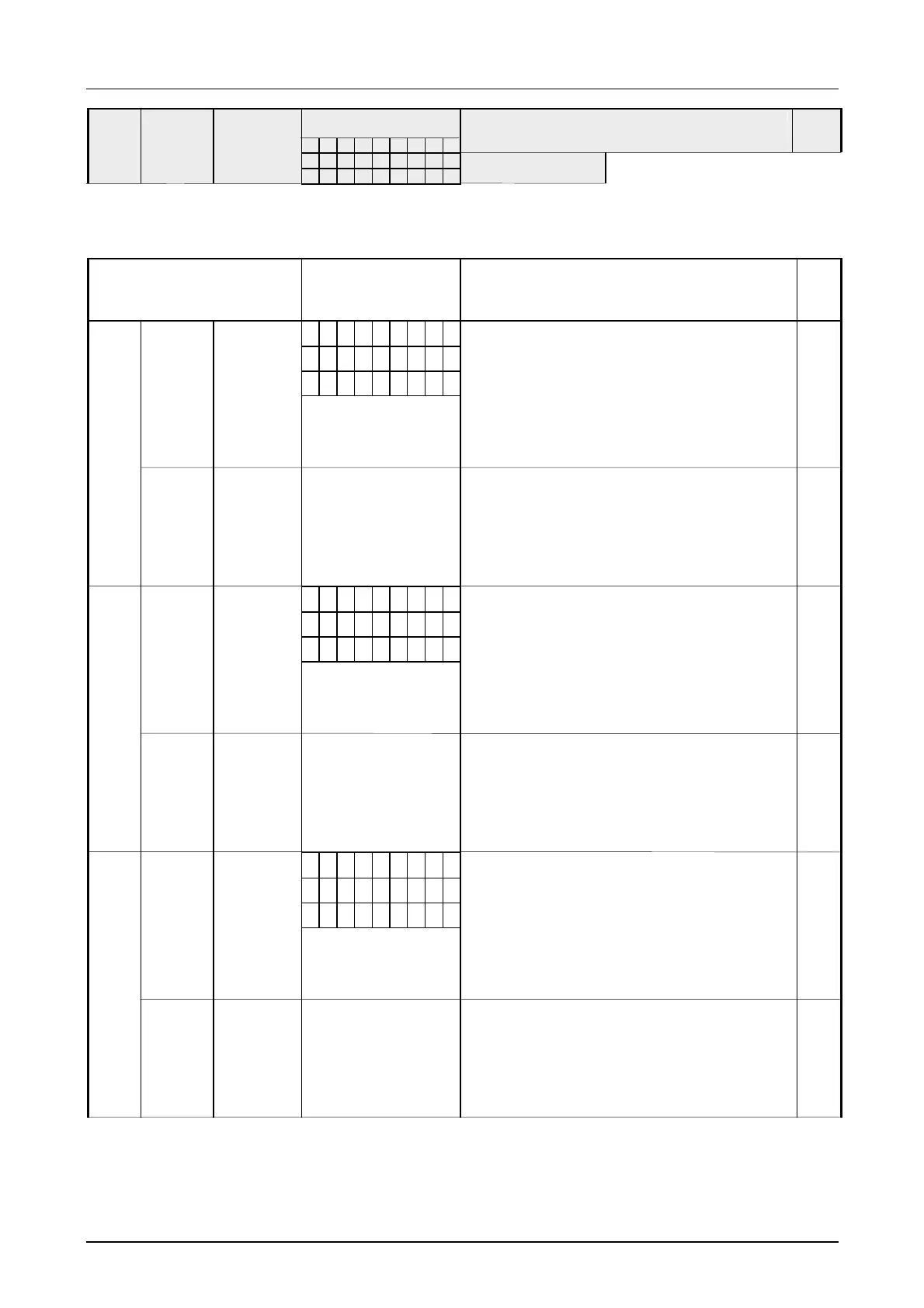

Command

Operand

Parameter

Status word

Function

Length

in

BR CC1 CC0 OV OS OR STA RLO /FC

words

: Instruction depends on

: Instruction influences

HB103E - Rev. 05/45 12-27

Combination instructions (Bit)

Combination instructions

with bit operands

Status word Examining the signal state of the addressed

instruction and gating the result with the RLO

according to the appropriate logic function.

A

BR CC1 CC0 OV OS OR STA RLO /FC

AND operation at signal state "1"

I/Q a.b

0.0 ... 127.7

- - - - - Y - Y Y Input/output 1/2

M a.b

0.0 ... 1023.7

- - - - - Y Y Y 1 Bit memory 1/2

L a.b

0.0 ... 1043.7

Local data bit 2

DBX a.b

0.0 ... 8191.7

Data bit 2

DIX a.b

0.0 ... 8191.7

Instance data bit 2

c [AR1,m]

register-indirect, area-internal (AR1) 2

c [AR2,m]

register-indirect, area-internal (AR2) 2

[AR1,m]

area-crossing (AR1) 2

[AR2,m]

area-crossing (AR2) 2

Parameter

via parameters 2

AN

BR CC1 CC0 OV OS OR STA RLO /FC

AND operation of signal state "0"

I/Q a.b

0.0 ... 127.7

- - - - - Y - Y Y Input/output 1/2

M a.b

0.0 ... 1023.7

- - - - - Y Y Y 1 Bit memory 1/2

L a.b

0.0 ... 1043.7

Local data bit 2

DBX a.b

0.0 ... 8191.7

Data bit 2

DIX a.b

0.0 ... 8191.7

Instance data bit 2

c [AR1,m]

register-indirect, area-internal (AR1) 2

c [AR2,m]

register-indirect, area-internal (AR2) 2

[AR1,m]

area-crossing (AR1) 2

[AR2,m]

area-crossing (AR2) 2

Parameter

via parameters 2

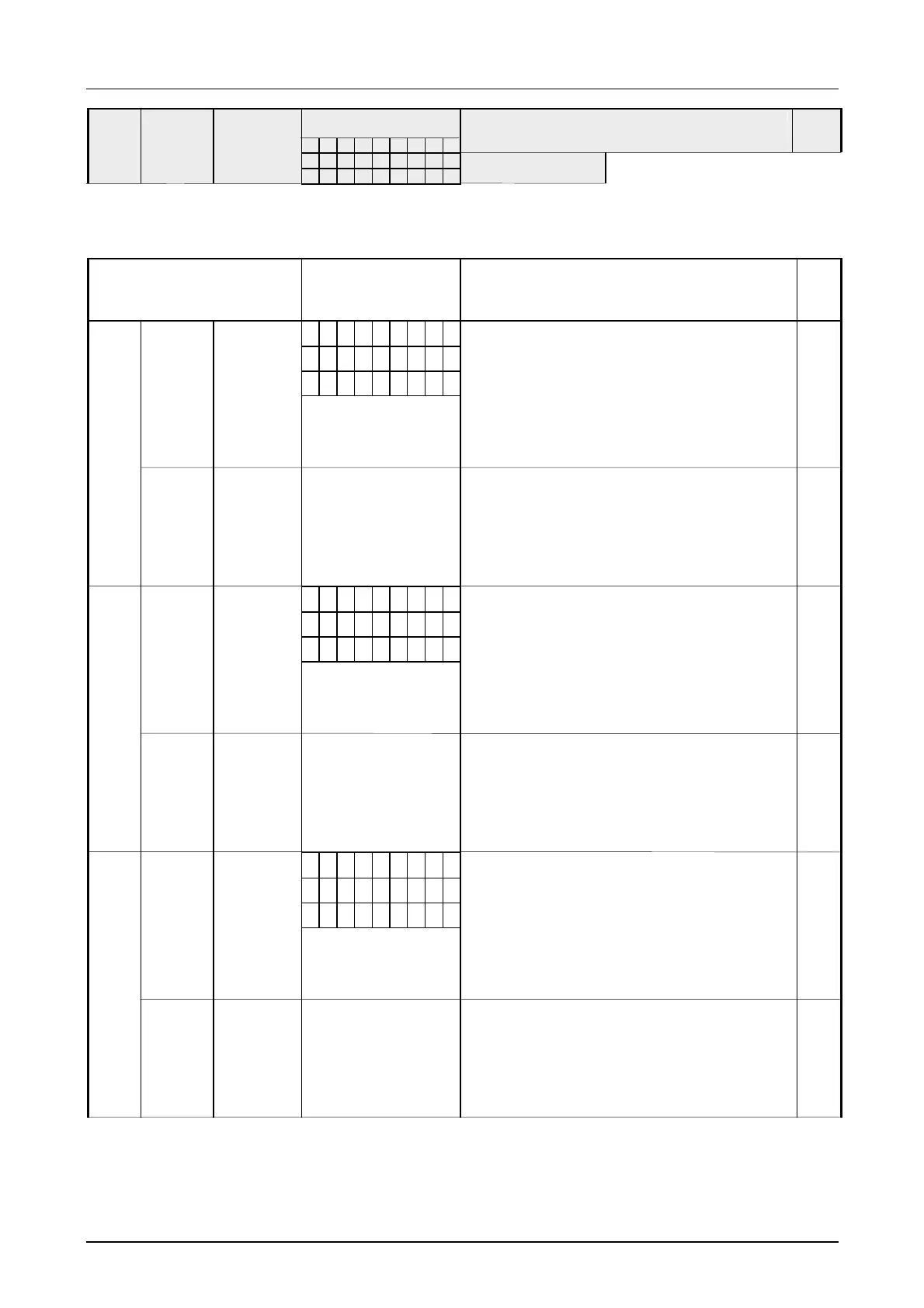

O

BR CC1 CC0 OV OS OR STA RLO /FC

OR operation at signal state "1"

I/Q a.b

0.0 ... 127.7

- - - - - - - Y Y Input/output 1/2

M a.b

0.0 ... 1023.7

- - - - - 0 Y Y 1 Bit memory 1/2

L a.b

0.0 ... 1043.7

Local data bit 2

DBX a.b

0.0 ... 8191.7

Data bit 2

DIX a.b

0.0 ... 8191.7

Instance data bit 2

c [AR1,m]

register-indirect, area-internal (AR1) 2

c [AR2,m]

register-indirect, area-internal (AR2) 2

[AR1,m]

area-crossing (AR1) 2

[AR2,m]

area-crossing (AR2) 2

Parameter

via parameters 2

Loading...

Loading...