Manual VIPA CPU 21x Chapter 10 Deployment CPU 21xSER-2

HB103E - Rev. 05/45 10-3

Protocols and Procedures

The CPU 21x-2BS02 supports the following protocols and Procedures:

• ASCII communication

• STX/ETX

• 3964(R) mit RK512

ASCII data communication is one of the simple forms of data exchange.

Incoming characters are transferred 1 to 1.

To ensure that messages can be divided into logical parts the 'character

delay time‘ (ZVZ) of the receiver must be matched by the transmitter. The

ZVZ is specified in milliseconds (ms) and it must be larger than or equal to

2ms.

On the transmitter the equivalent of the receiver's character delay time is

the 'time from reception of job ‘ (ZNA). These two times can be used to

establish a simple serial PLC communication path. Any transmit job is only

acknowledged with 'job completed without errors' (AFOF) when the data

was transmitted and the ZNA has expired.

If ZNA is set to 0, the send sequence has to be controlled via the user

application.

STX/ETX is a simple protocol with start and end ID, where STX stands for

Start of Text and ETX for End of Text.

The STX/ETX procedure is suitable for the transfer of ASCII characters

(20h…7Fh). It does not use block checks (BCC). Any data transferred from

the periphery must be preceded by an Start followed by the data characters

and the end character.

The effective data which includes all the characters between Start and End

are transferred to the CPU when the End has been received.

When data is send from the CPU to a peripheral device, any user data is

handed to the CPU 21x-2BS02 where transferred to the communication

partner.

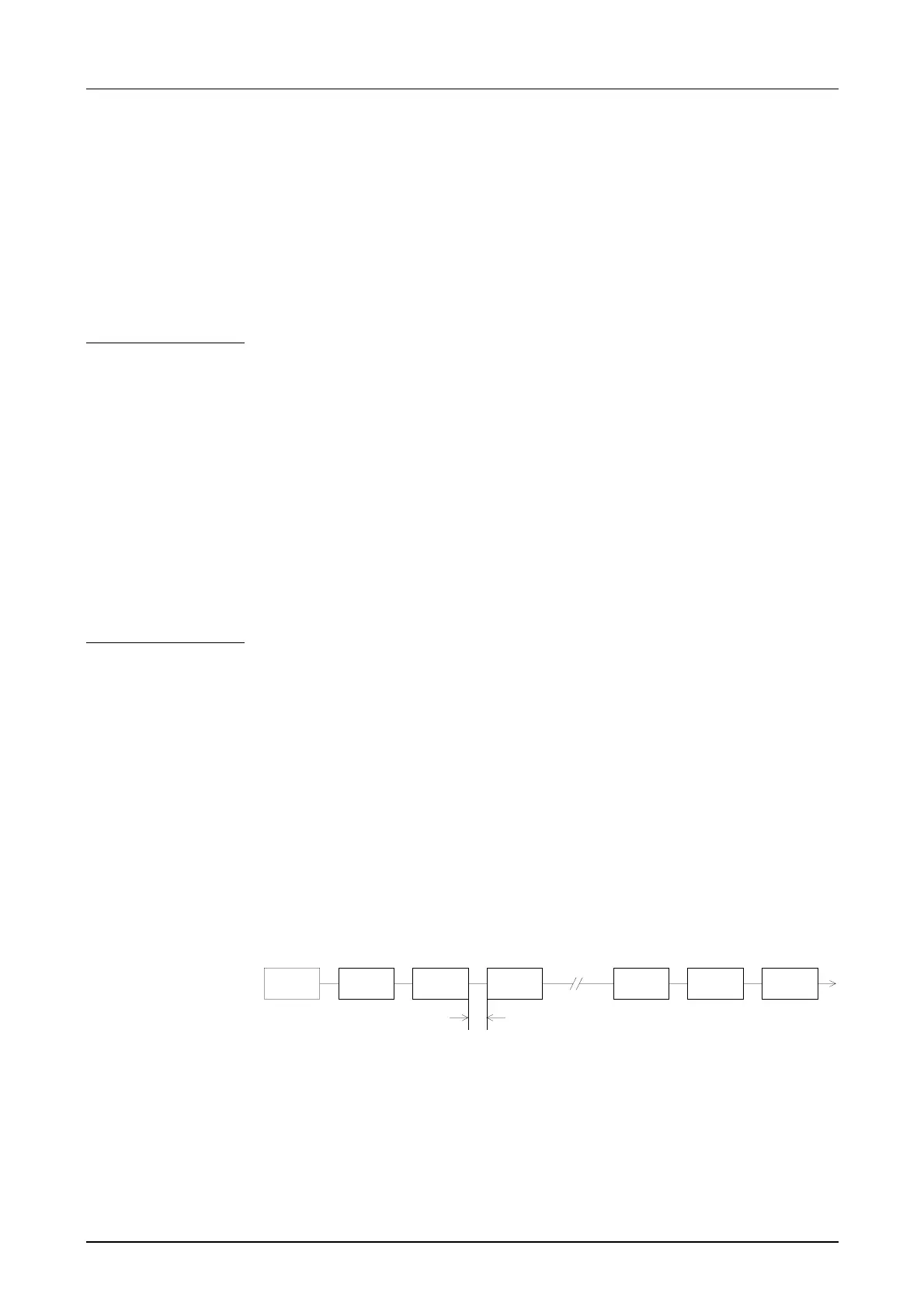

Message structure:

STX2 Z1 Z2 Zn ETX1 ETX2

ZVZ

STX1

You may define up to 2 start and end characters.

You may work with 1, 2 or no Start- and with 1, 2 or no End-ID. As Start-

res. End-ID all Hex values from 01h to 1Fh are permissible. Characters

above 1Fh are ignored. In the user data, characters below 20h are not

allowed and may cause errors. The number of Start- and End-IDs may be

different (1 Start, 2 End res. 2 Start, 1 End or other combinations). If no

End-ID is defined, all read characters are transferred to the CPU after a

parameterizable character delay time (Timeout).

Übersicht

ASCII

STX/ETX

Loading...

Loading...