Chapter 1 Principles Manual VIPA CPU 21x

1-6 HB103E - Rev. 05/45

Function security of the VIPA CPUs

The CPUs include security mechanisms like a Watchdog (100ms) and a

parameterizable cycle time surveillance (parameterizable min. 1ms) that

stop res. execute a RESET at the CPU in case of an error and set it into a

defined STOP state.

The VIPA CPUs are developed function secure and have the following

system properties:

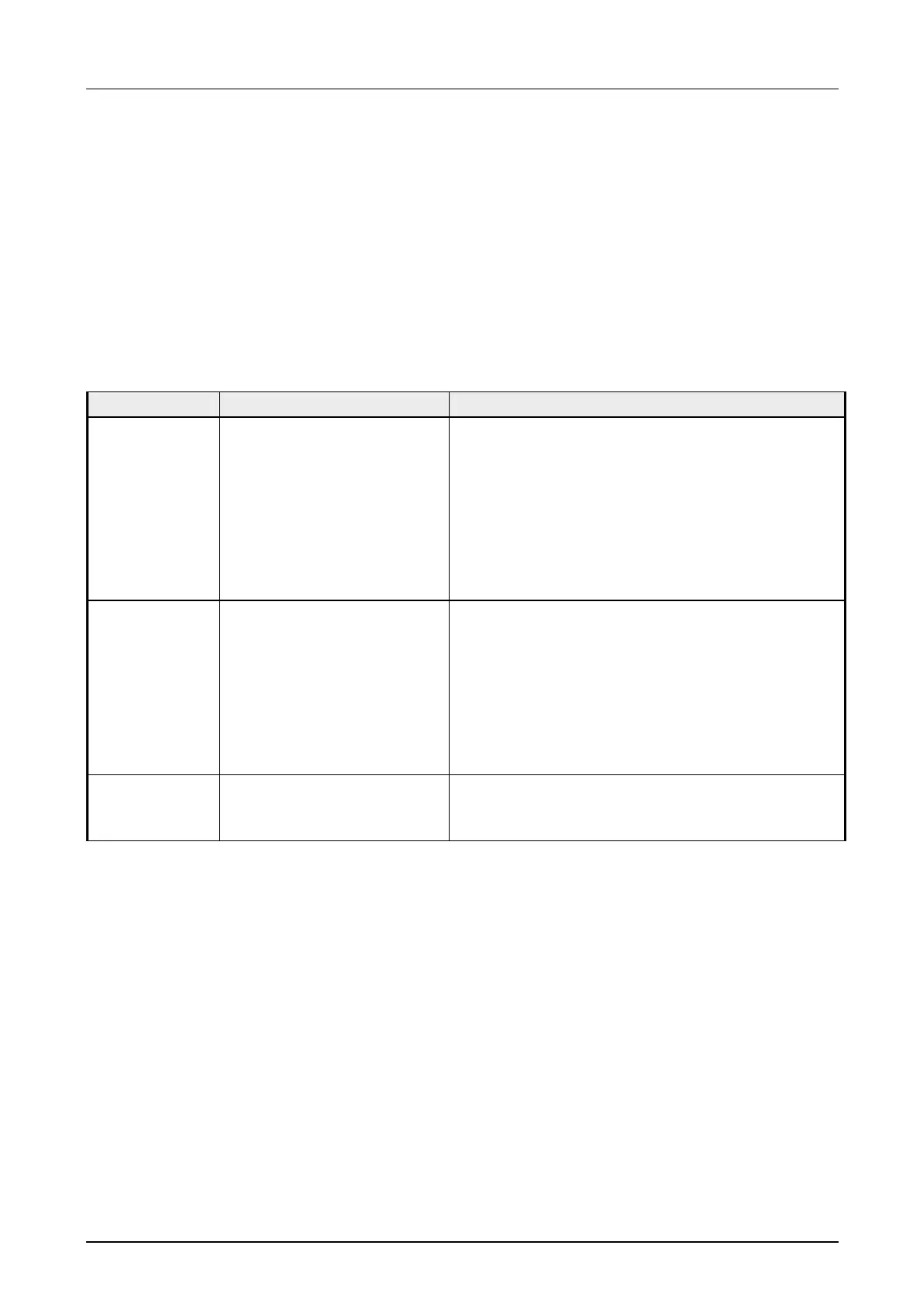

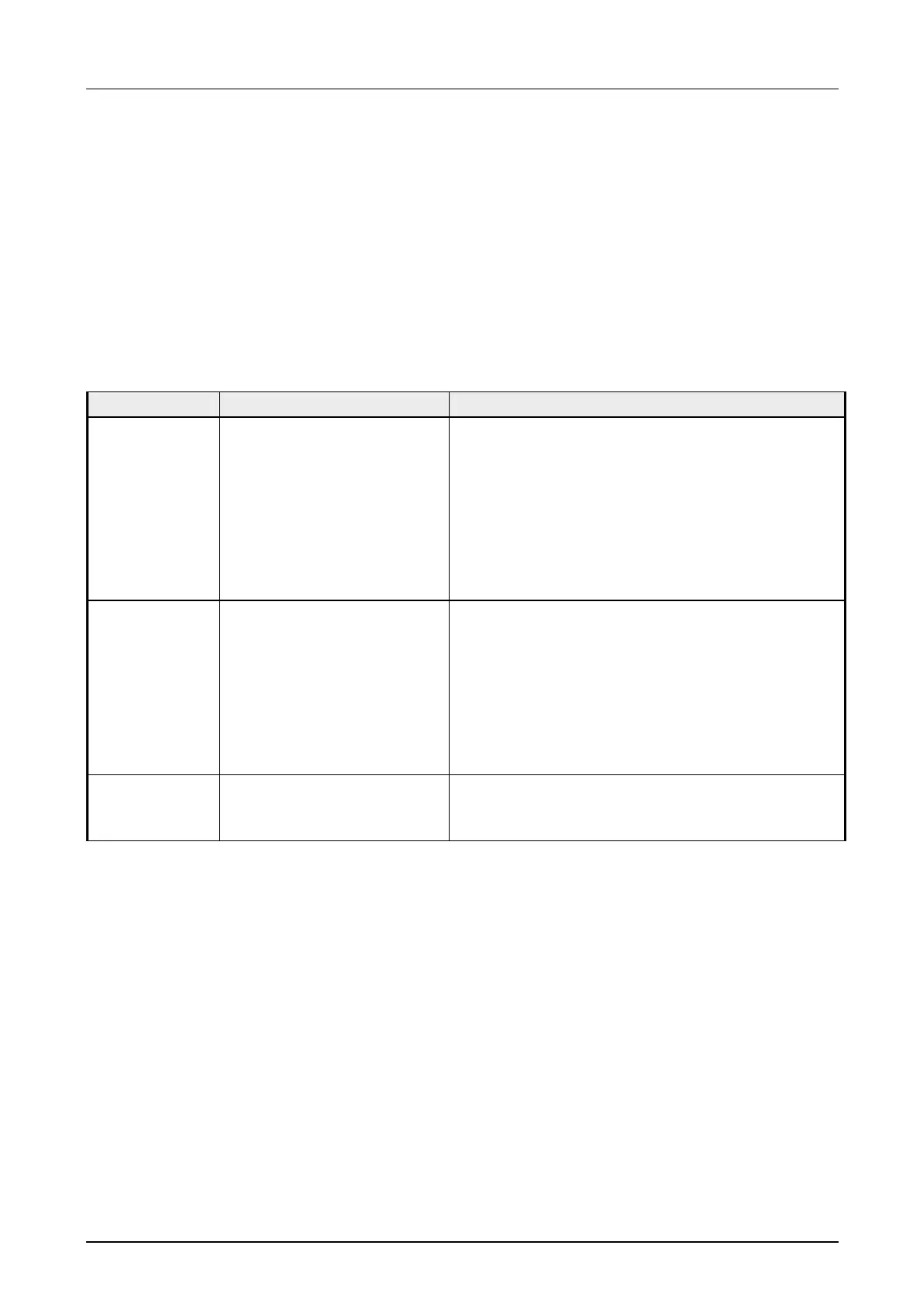

Event concerns Effect

RUN → STOP

general

BASP (Befehls-Ausgabe-Sperre, i.e. command

output lock) is set.

central digital outputs The outputs are set to 0V.

central analog outputs The voltage supply for the output channels is

switched off.

decentral outputs The outputs are set to 0V.

decentral inputs The inputs are read constantly from the slave and

the recent values are put at disposal.

STOP → RUN

res. Power on

general First the PII is deleted, the call of the OB100

follows. After the execution of the OB, the BASP is

set back and the cycle starts with:

Delete PIO → Read PII → OB1.

central analog outputs The behavior of the outputs at restart can be

preset.

decentral inputs The inputs are read constantly from the slave and

the recent values are put at disposal.

RUN general The program execution happens cyclically and can

therefore be foreseen:

Read PII → OB1 → Write PIO.

PII: = Process image inputs

PIO: = Process image outputs

Loading...

Loading...