MIPI CSI-2 RX Subsystem v4.0 43

PG232 July 02, 2019 www.xilinx.com

Chapter 3: Designing with the Subsystem

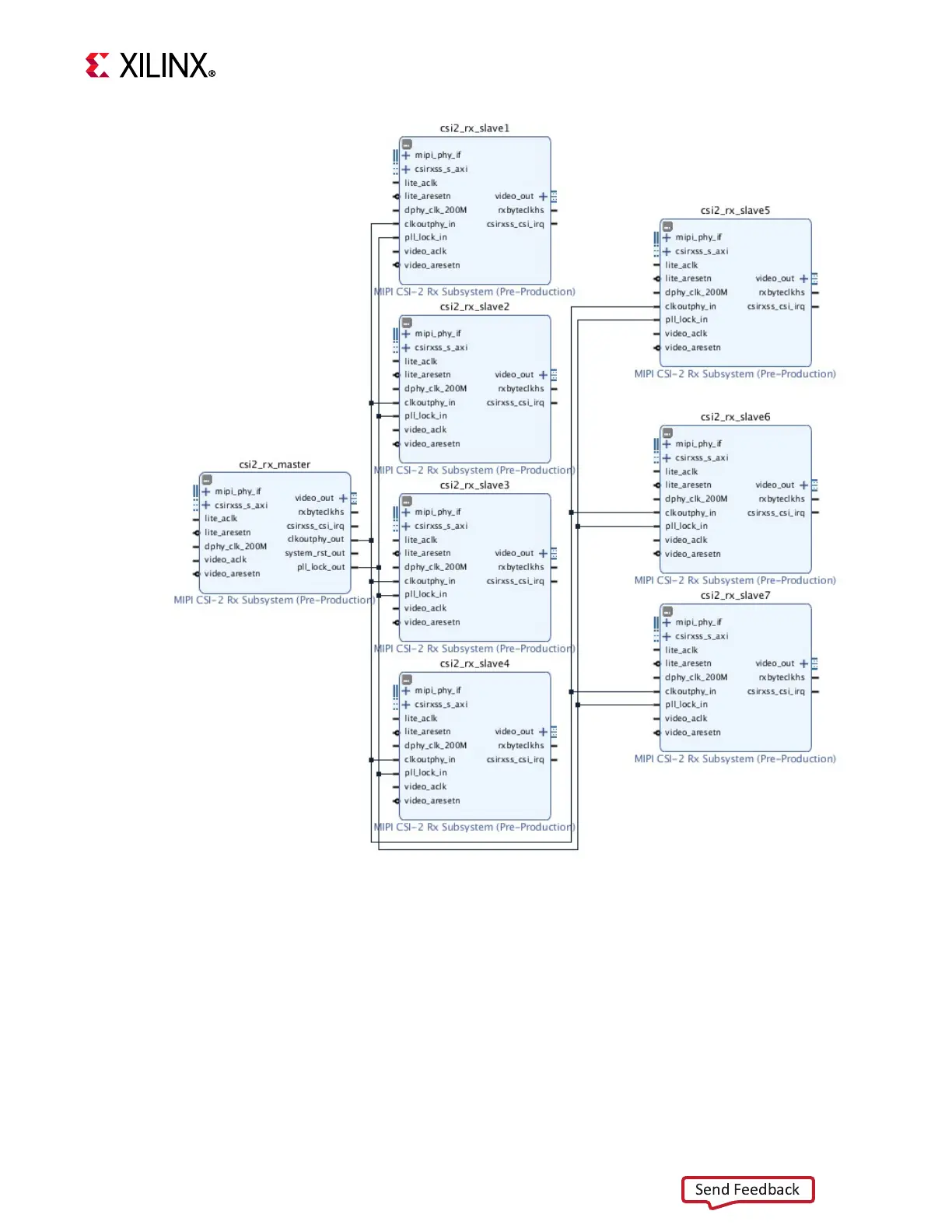

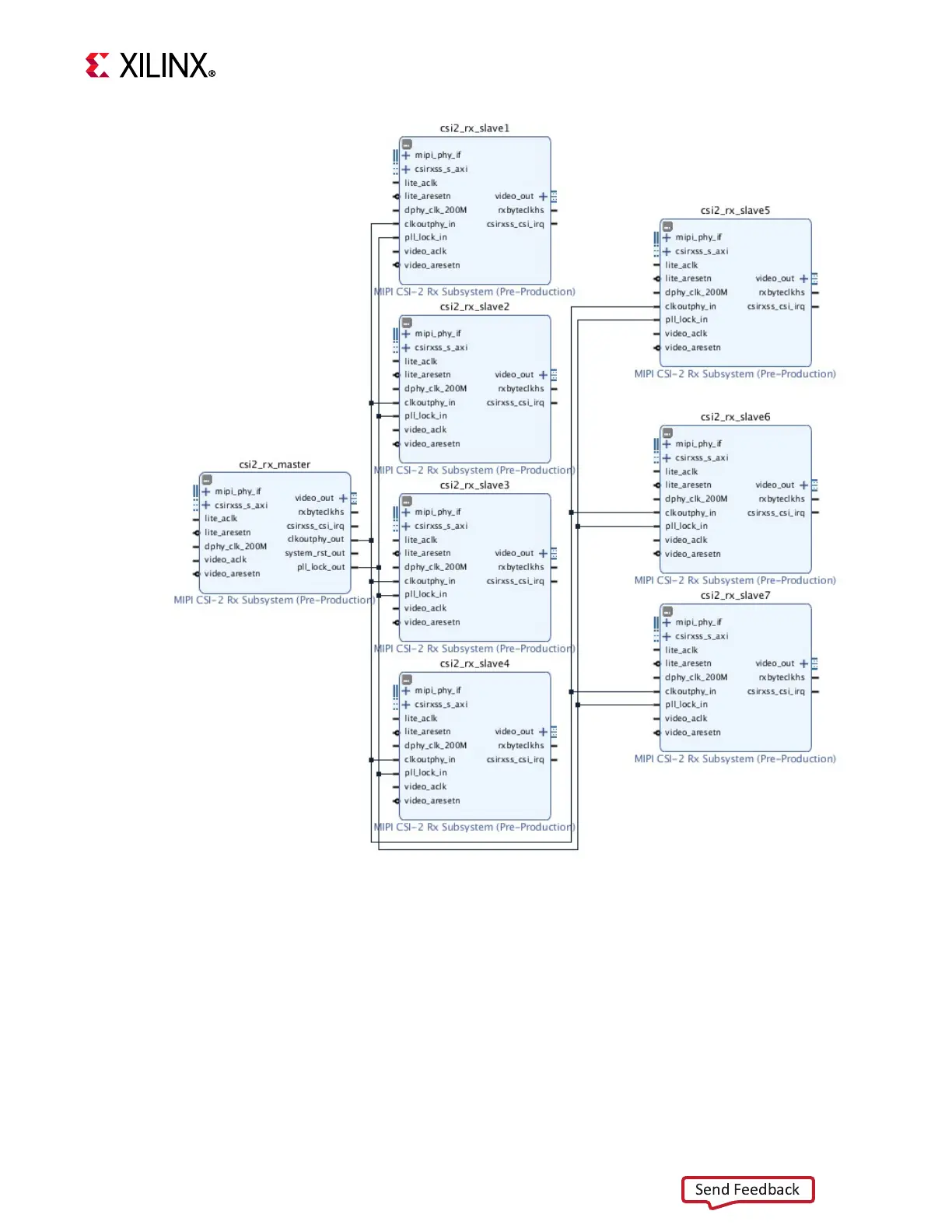

Maximum number of MIPI CSI-2 interfaces which can be connected to single HP IO bank

depends on the number of clock capable pins available on that bank. For example, HP IO

Bank 67 on ZCU102 UltraScale+ device has eight clock capable pins as shown below, which

allows eight MIPI CSI-2 RX interfaces to use same HP IO Bank.

X-Ref Target - Figure 3-5

Figure 3-5: MIPI CSI-2 RX Subsystem Core Shared Logic Use Case for Single I/O Bank

Loading...

Loading...