MOTIF XS6/MOTIF XS7/MOTIF XS8

64

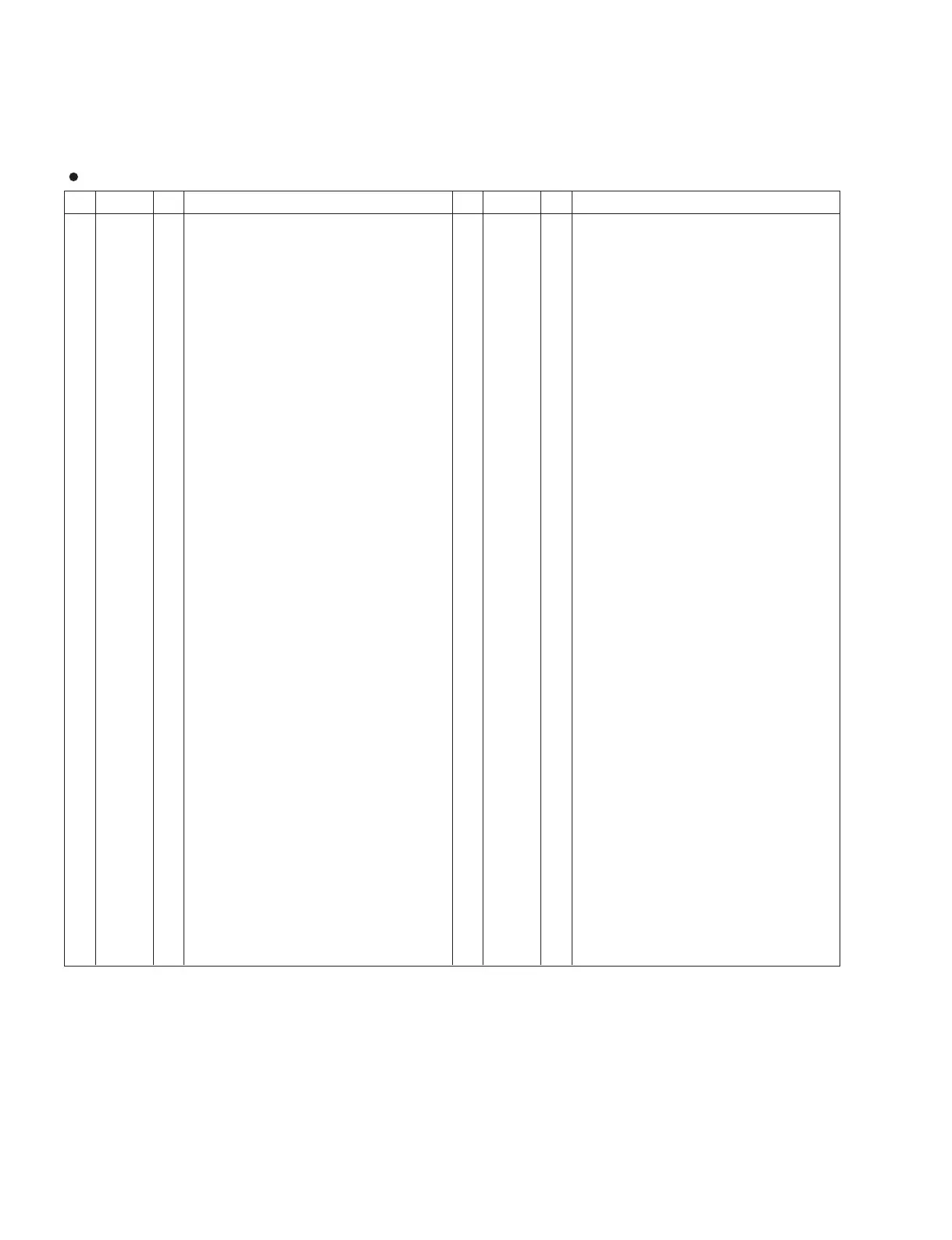

MLAN: IC101,102 (XS8 only)

PIN

NO.

I/O

FUNCTION

NAME

PIN

NO.

I/O

FUNCTIONNAME

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

VDD

JUMPSEL

TABLESEL

SCANENB

ATPGENE

VSS

PLLTEST

PLLRESN

PLLVSS

MVDD

PLLVSS

AVDD

PLLCHGO

LPVSS

PLLBP

V

SS

EXTCLK1

VDD

EXTCLK0

VDD

TESTENB

TESTIP0

TESTIP1

TESTIP2

VSS

VDD

PHASEMATCH

VSS

XI

XO

VSS

BOBCLK

BOLRCK

BOFMT2

BOFMT1

BOFMT0

VDD

BIFMT2

BIFMT1

BIFMT0

V

SS

B_WCK_OK

BIBCLK

BILRCK

VDD

BISFTUP1

BISFTUP0

BIBYPASS

BODAMPN

VSS

-

I

I

I

I

-

I

I

-

-

-

-

O

I

I

-

I

-

O

-

I

I

I

I

-

-

I

-

I

O

-

I/O

I/O

I

I

I

-

I

I

I

-

O

I/O

I/O

-

I

I

I

I

-

Power supply +3.3V

Digital PLL sensitivity select

Digital PLL capture speed select

Test pin (GND connect with normal)

Test pin (GND connect with normal)

Ground

Test pin (GND connect with normal)

Reset input (Master clock PLL)

Ground (Master clock PLL)

Power supply (Digital)

Ground (Master clock PLL)

Power supply (Analog)

Output signal for external filter of master clock PLL

Input signal for external filter of master clock PLL

Test pin (GND connect with normal)

Ground (Digital)

Input for master clock PLL

Power supply +3.3V (Digital)

Output XO terminal

Power supply +3.3V

Test pin (GND connect with normal)

Test pin (GND connect with normal)

Test pin (GND connect with normal)

Test pin (GND connect with normal)

Ground

Power supply +3.3V

Phase muching mode ON/OFF

Ground

Crystal osc. input

Crystal osc. output

Ground

Bit clock input/output for B block data output

Word clock input/output for B block data output

Data output format for B block

Data output format for B block

Data output format for B block

Power supply +3.3V

Data input format for B block

Data input format for B block

Data input format for B block

Ground

Lock frag for B block input/output

Bit clock input/output for B block data input

Word clock input/output for B block data input

Power supply +3.3V

Shiftup for B block input data

Shiftup for B block input data

Bypass for B block input/output

Damp output data for B block

Ground

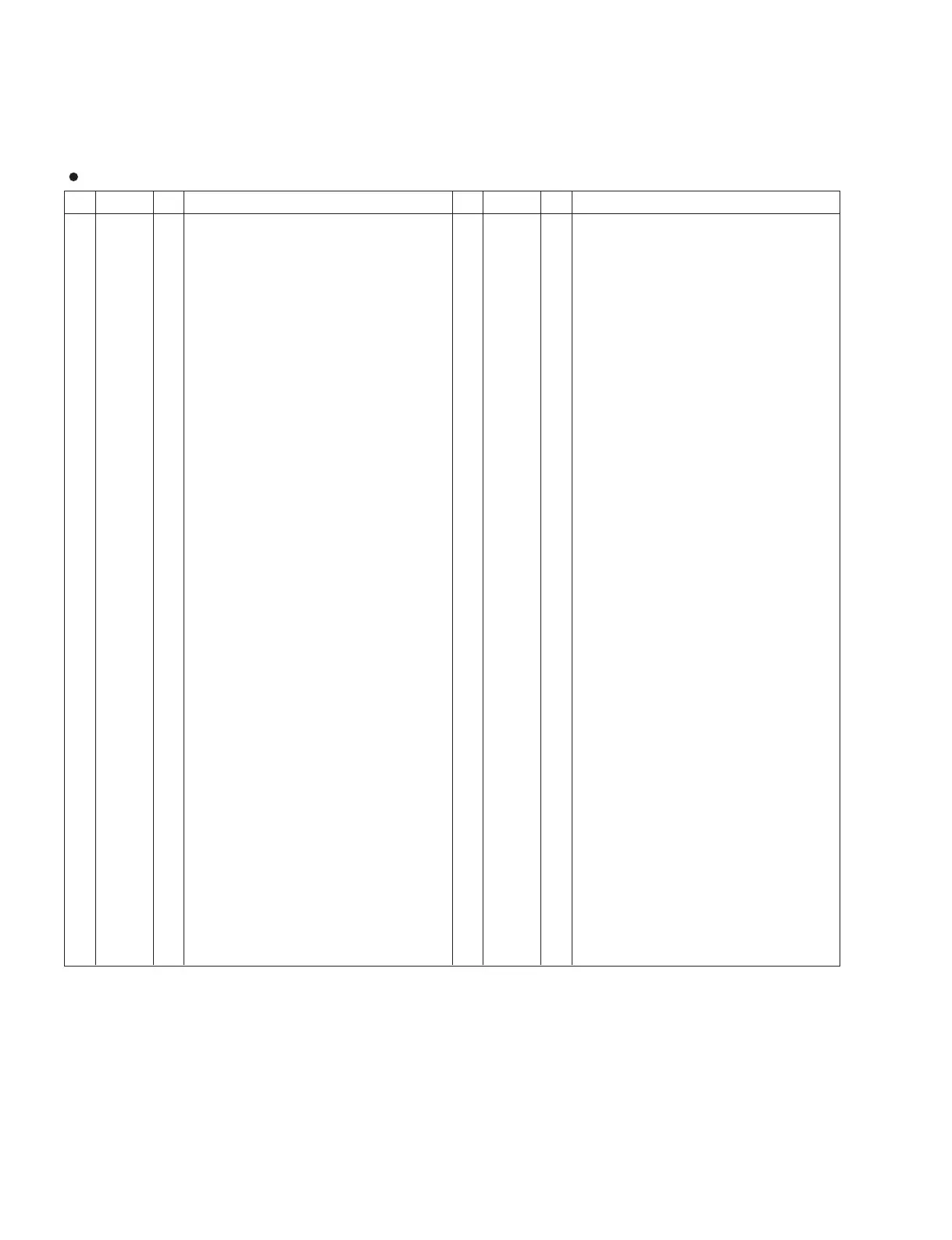

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

V

DD

BOSD3

BOSD2

BOSD1

BOSD0

V

SS

BISD3

BISD2

BISD1

BISD0

V

DD

DIVSEL1

DIVSEL0

DIVCLK0

V

SS

AOSD3

AOSD2

AOSD1

AOSD0

V

DD

AISD3

AISD2

AISD1

AISD0

V

SS

V

DD

AODAMPN

AIBYPASS

AISFTUP0

AISFTUP1

V

SS

AILRCK

AIBCLK

A_WCK_OK

V

DD

AIFMT0

AIFMT1

AIFMT2

V

SS

AOFMT0

AOFMT1

AOFMT2

AOLRCK

AOBCLK

V

DD

REGDAT

REGCLK

REGENB

ICN

V

SS

-

O

O

O

O

-

I

I

I

I

-

I

I

O

-

O

O

O

O

-

I

I

I

I

-

-

I

I

I

I

-

I/O

I/O

O

-

I

I

I

-

I

I

I

I/O

I/O

-

I

I

I

I

-

Power supply +3.3V

Serial data output for B block

Serial data output for B block

Serial data output for B block

Serial data output for B block

Ground

Serial data input for B block

Serial data input for B block

Serial data input for B block

Serial data input for B block

Power supply +3.3V

Clock frequency for DIVCLK0 terminal

Clock frequency for DIVCLK0 terminal

Master clock output

Ground

Serial data output for A block

Serial data output for A block

Serial data output for A block

Serial data output for A block

Power supply +3.3V

Serial data input for A block

Serial data input for A block

Serial data input for A block

Serial data input for A block

Ground

Power supply +3.3V

Damp output data for A block

Bypass for A block input/output

Shiftup for A block input data

Shiftup for A block input data

Ground

Word clock input/output for A block input data

Bit clock input/output for A block input data

Lock frag for A block input/output

Power supply +3.3V

Data input format for A block

Data input format for A block

Data input format for A block

Ground

Data output format for A block

Data output format for A block

Data output format for A block

Word clock input/output for A block output data

Bit clock input/output for A block output data

Power supply +3.3V

Data input for serial register

Clock input for serial register

Enable signal input for serial register

Initial clear input

Ground

S1L54423F21C000 (X4072A00) SRC16 (Gate Array)

Loading...

Loading...