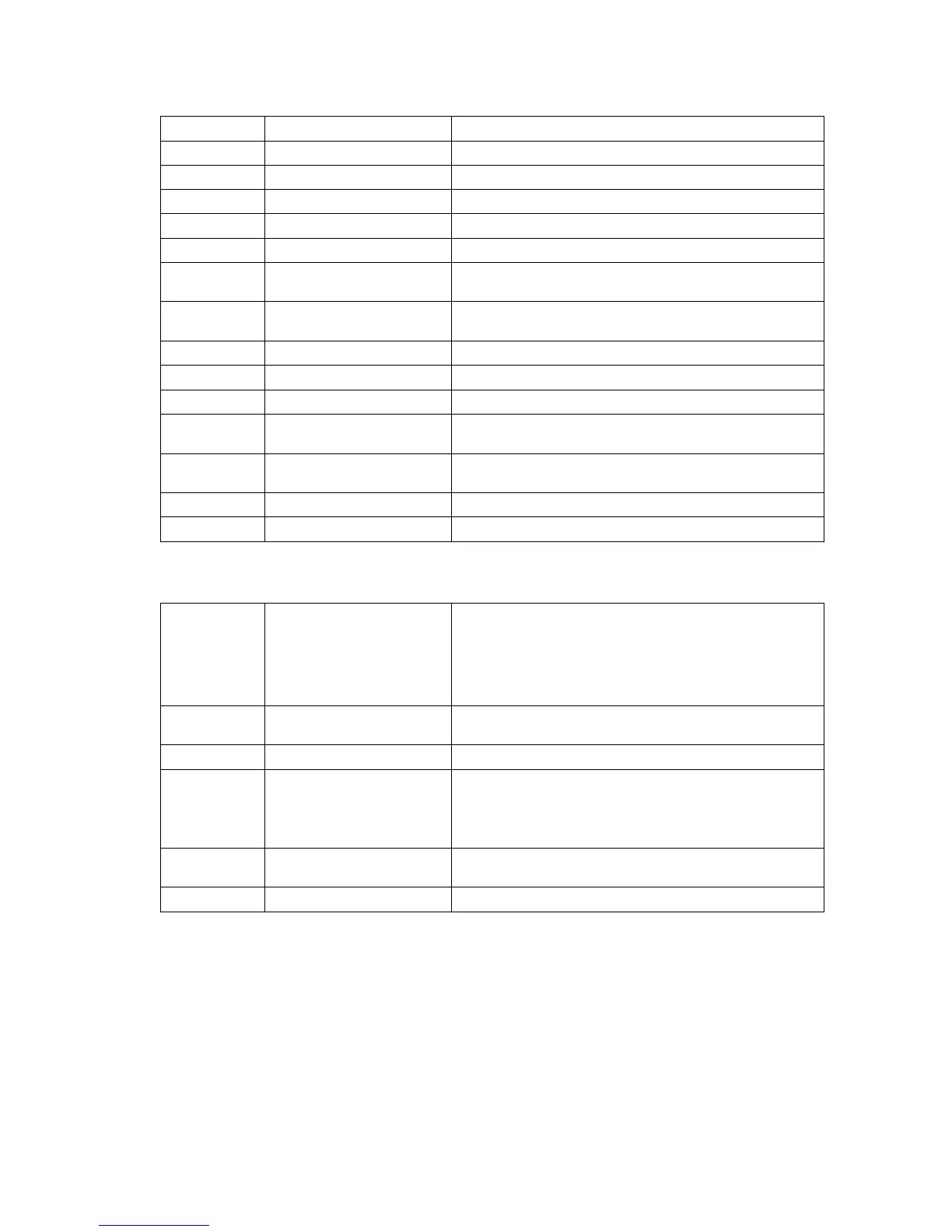

Specifications | 250

QV24 Quad V.24 asynchronous data interface

General

Interface ITU-T V.24/EIA/TIA RS-232E

Bandwidth allocation 8-120 kbit/s in 8 kbit/s steps (dependent on rate selected)

Control line allocation 8 kbit/s

Maximum line length 10 metres

Data clamp Mark hold when out of sync.

Control line clamp Off when loss of sync.

Clock Internally generated from 2.048 MHz system clock

(synchronized at both ends)

Async

parameters

Transparent mode Operation is completely transparent but limited to 0-600 bit/s

Standard mode data bits 7,8

Standard mode parity Transparent (enable / disable)

Standard mode stop bits 1,2

Data rates (bit/s) 300, 600, 1200, 2400, 4800, 7200, 9600, 12800, 14400,

19200, 23040, 28800, 38400, 57600 and 115200

Control

signals

End-to-end CTS-RTS, DSR-DTR

Diagnostics

Green LED RD data traffic

Yellow LED TD data traffic

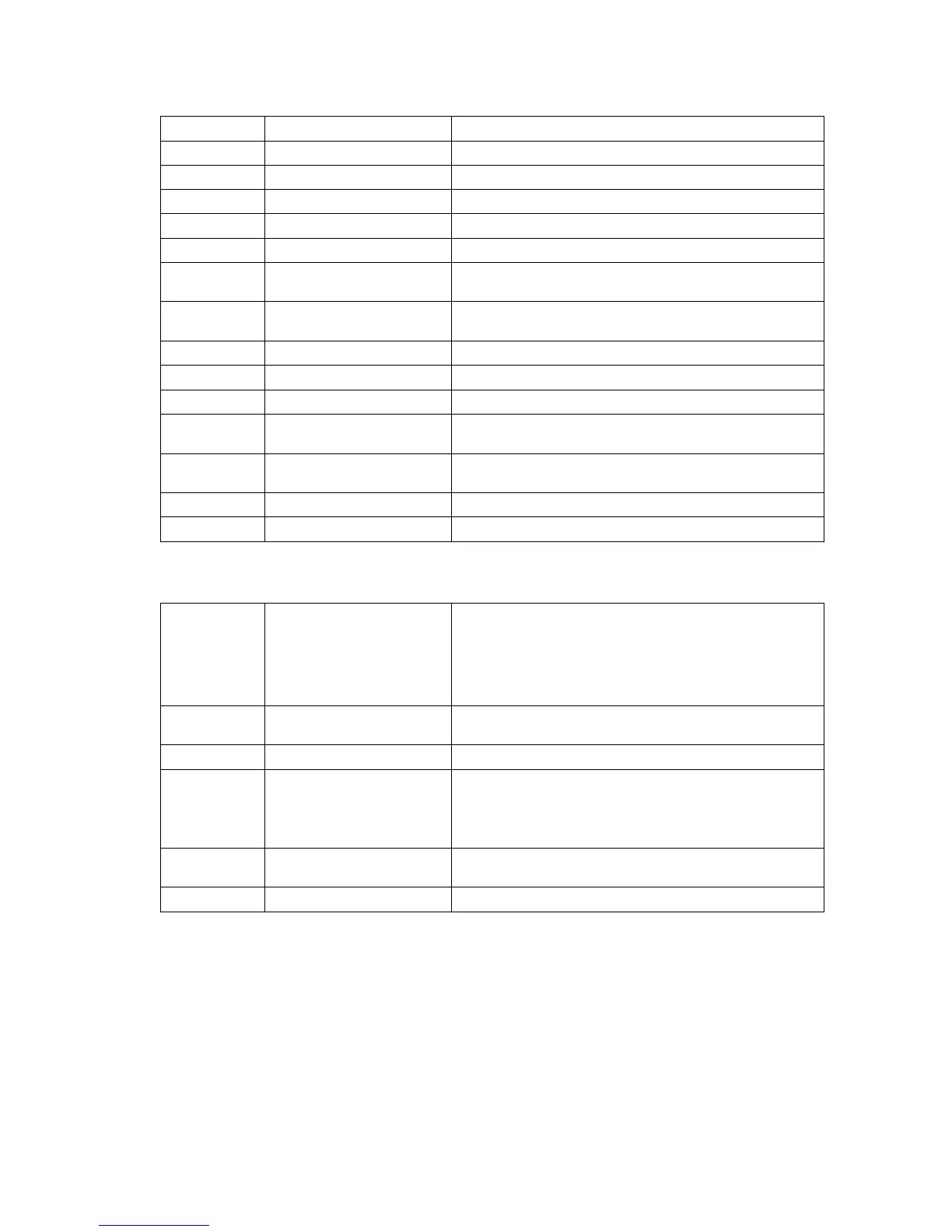

HSS Single high speed synchronous data interface

General

Interfaces ITU-T V.24 EIA/TIA RS-232E

ITU-T V.35

ITU-T V.36 EIA/TIA RS-449

ITU-T X.21

EIA/TIA 530

Bandwidth allocation 8-2048 kbit/s in 8 kbit/s steps (dependent on rate selected)

8 kbit/s for control lines

Maximum line length 3 metres

Clock Internally generated from 2.048 MHz system clock

(synchronized at both ends) on DCE to DCE mode.

Clock provided by external DCE when in DTE mode.

Remote DCE outputs clock-timed by incoming clock at DTE.

Diagnostics

Top Green LED On: Normal operation

Flashing: Loopback

Lower Green LED On: Normal operation

Loading...

Loading...