Appendix D-50 Product Overview Rev. A

Confidential

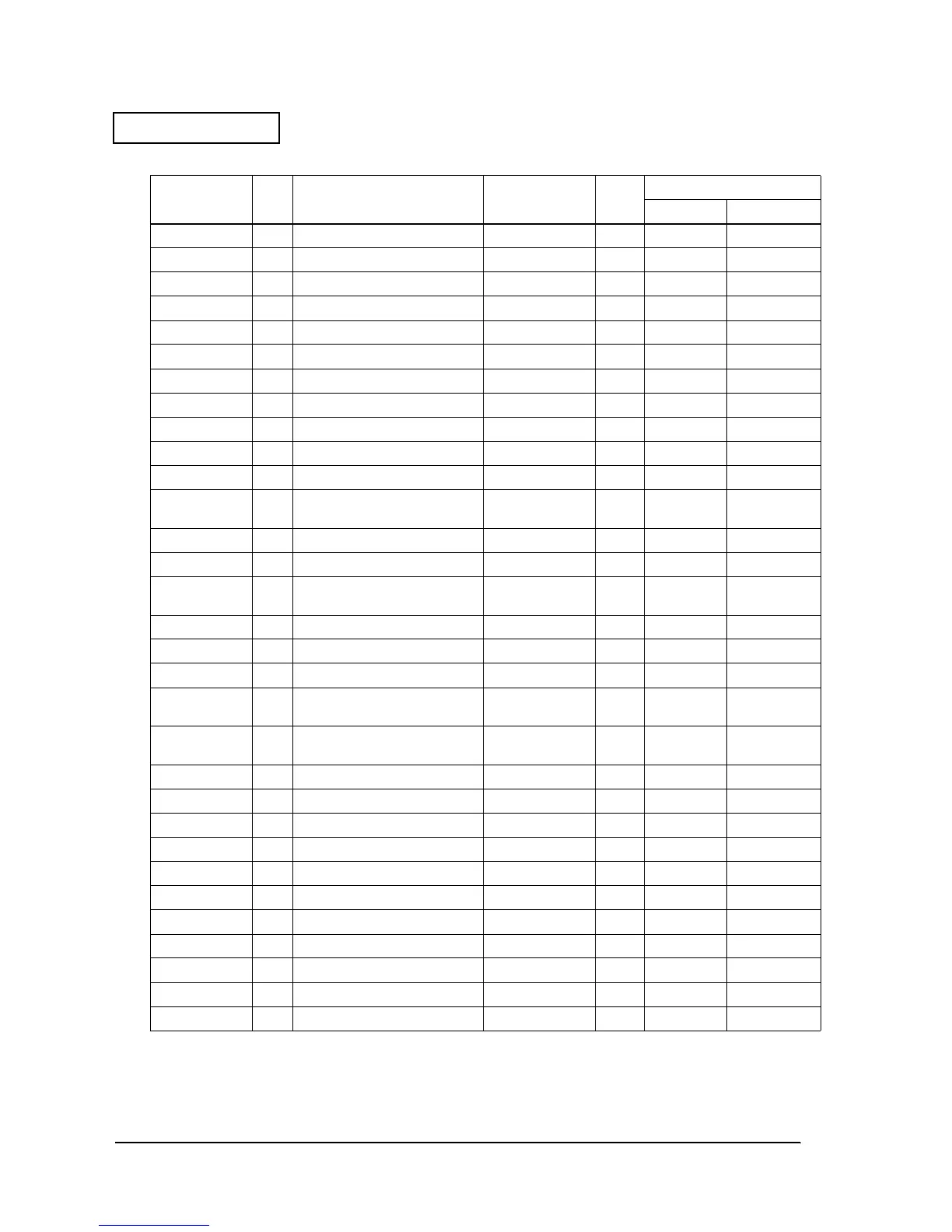

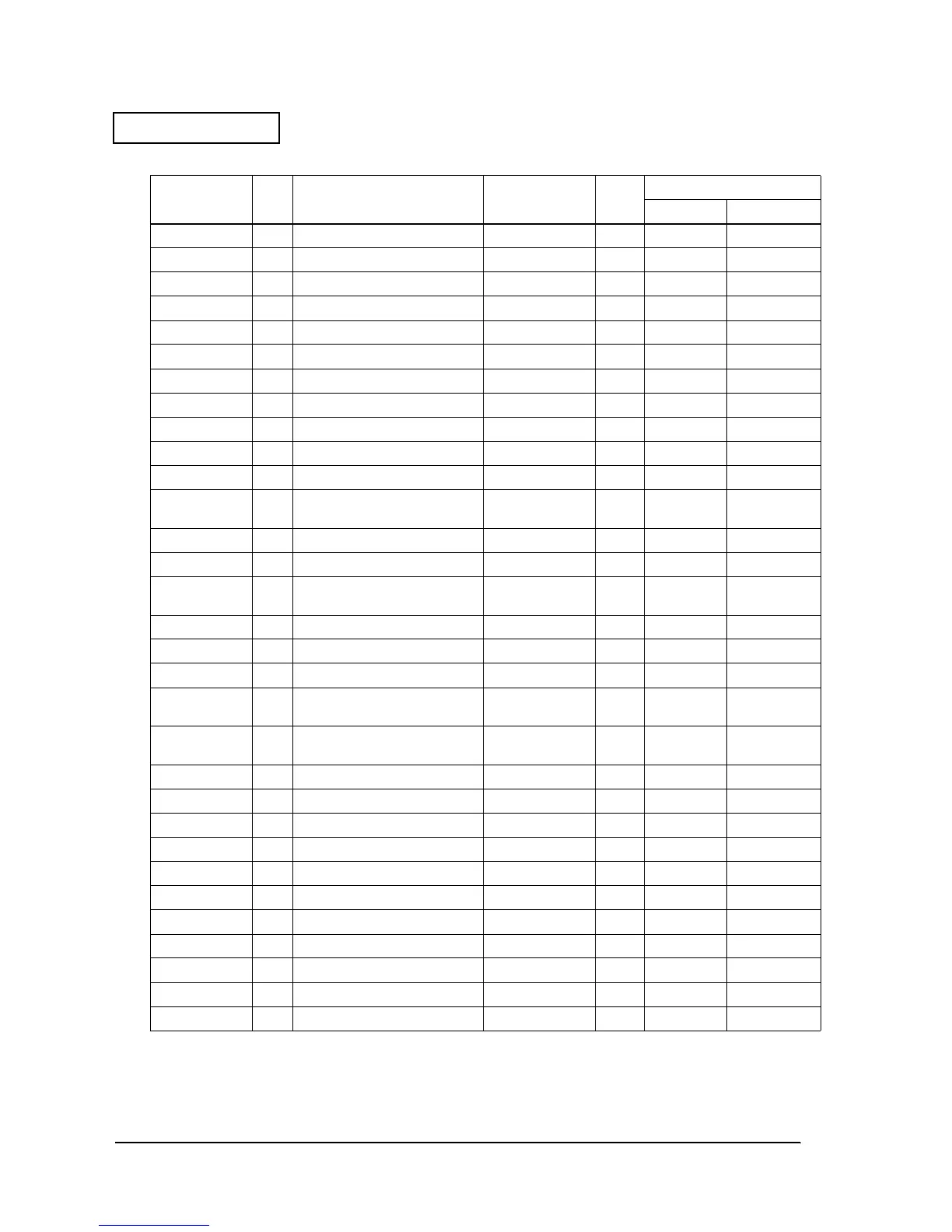

P41/A01 114 External address bus A1

10

P40/A00 115 External address bus A0

10

DVCC 116 VCC

PZ0 117 DSW1-1 DSW1-1 IN OFF ON

PZ1 118 DSW1-2 DSW1-2 IN OFF ON

PZ2 119 DSW1-3 DSW1-3 IN OFF ON

PZ3 120 DSW1-4 DSW1-4 IN OFF ON

PZ4 121 DSW1-5 DSW1-5 IN OFF ON

PZ5 122 DSW1-6 DSW1-6 IN OFF ON

PZ6 123 EJ memory WP signal EJ_WP OUT

PZ7 124 Power source LED LED_POWER OUT ON OFF

PH4/INT0 125 For future expansion, currently

pulled down

WAKE IN

PH0/TC0 126 DKD1 DKD1 OUT OFF ON

PH1/TC1 127 DKD2 DKD2 OUT OFF ON

PH2/TC2 128 Drawer sensor 1 DKDS1 IN Terminal

24V

Terminal GND

PH3/TC3 129 DSW1-7 DSW1-7 IN OFF ON

DVSS 130 GND

PG0/AN0 131 24 VDC monitor 24V_RD IN

PG1/AN1 132 Thermal head temperature

(TH_THERM)

TH_THERM IN

PG2/AN2 133 Impact head temperature

(IM_THERM)

IM_THERM IN

PG3/AN3 134 MICR data MIRD IN

PG4/AN4 135 TOF SLIP_TOF IN

PG5/AN5 136 BOF SLIP_BOF IN

PG6/AN6 137 Validation detector SLIP_VARI IN

PG7/AN7 138 Ejection detector SLIP_HAI IN

VREFH 139 VCC

VREFL 140 GND

ADVSS 141 GND

ADVCC 142 VCC

DAVSS 143 GND

DAVCC 144 VCC

TableD-7 CPU terminals and functions

Port (Terminal) Pin Description Circuit Signal I/O I/O Definition

Name No. Name

HL

Loading...

Loading...