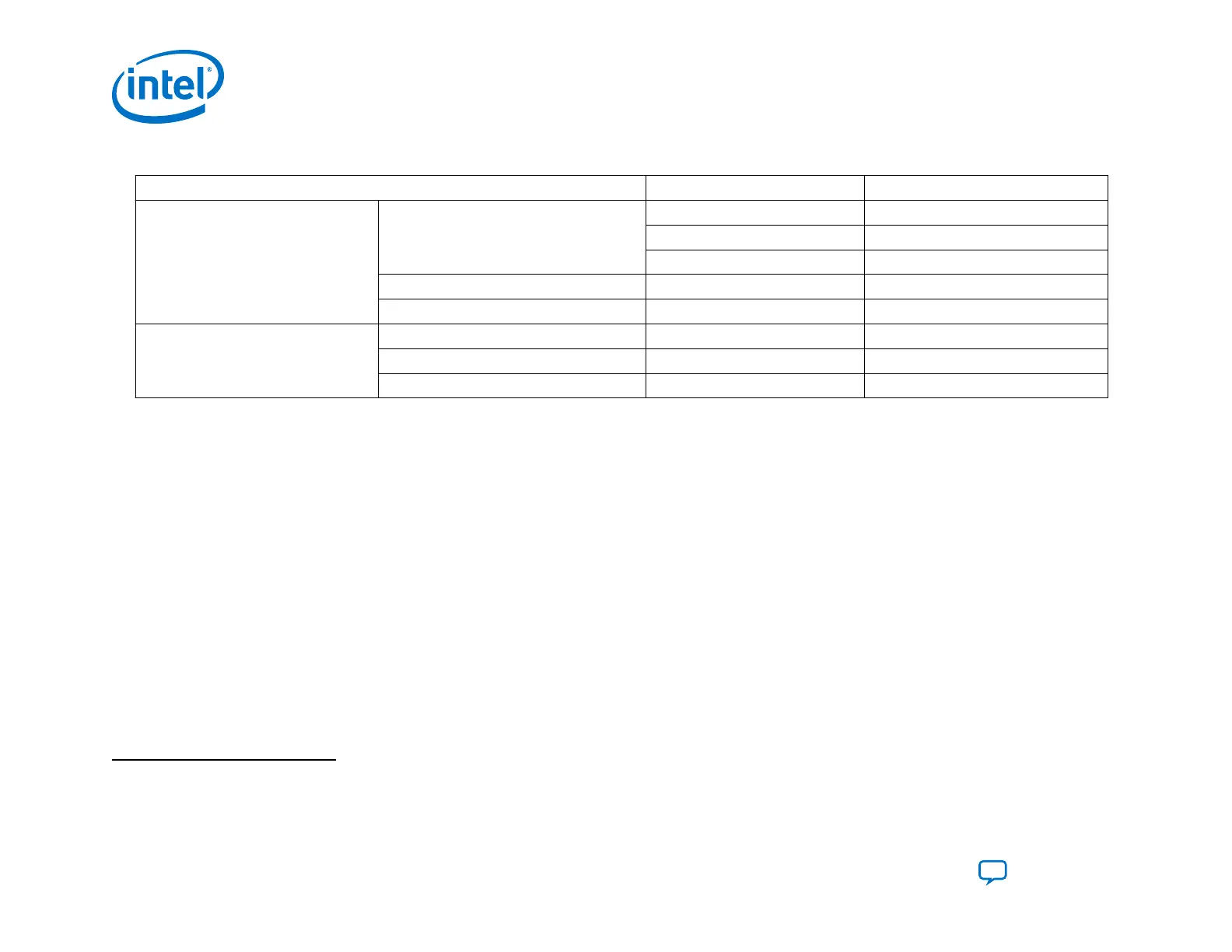

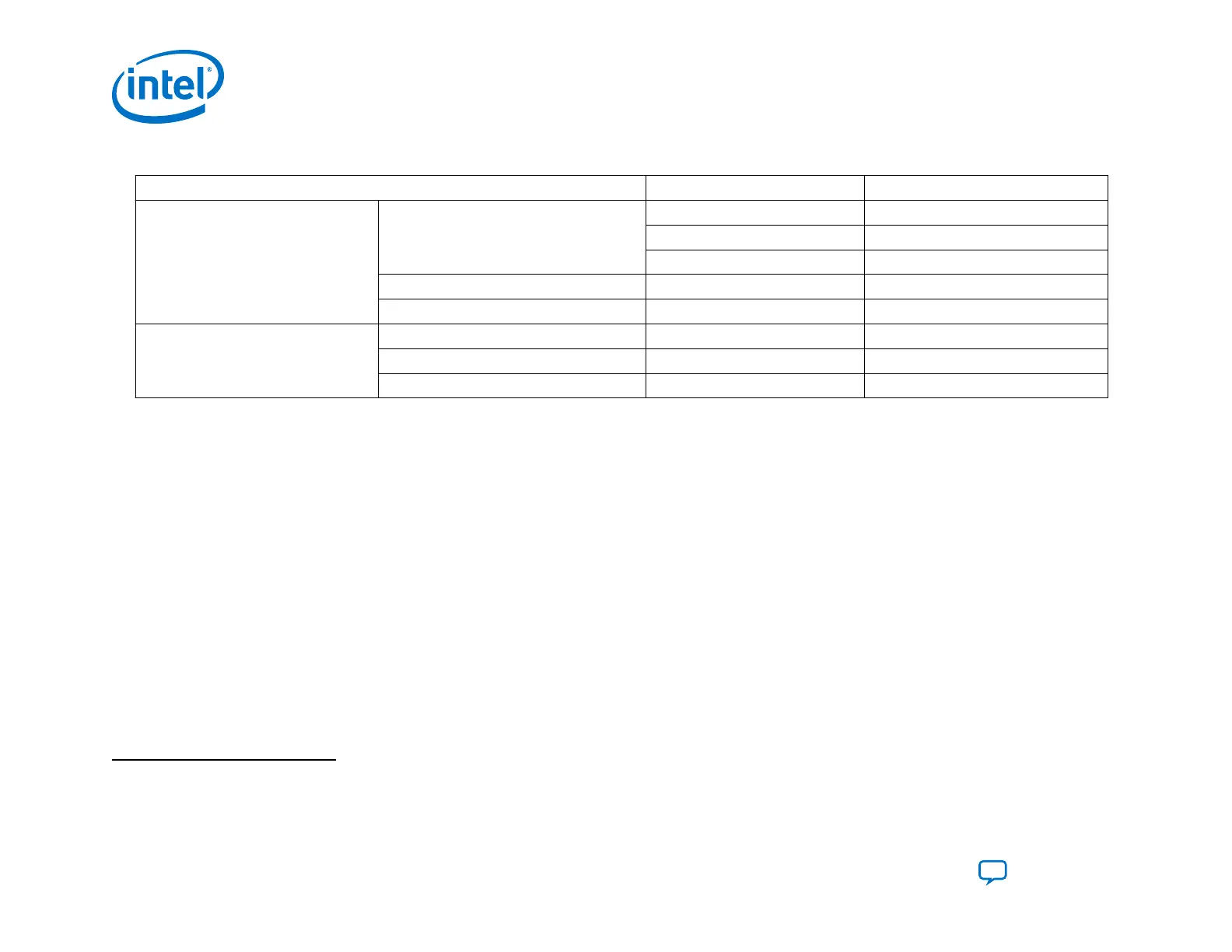

Table 1. Intel Agilex Configuration Data Width, Clock Rates, and Data Rates

Configuration Scheme Data Width (bits) MSEL[2:0]

Passive

Avalon-ST

32 000

16 101

8 110

JTAG 1 111

Configuration via Protocol (CvP) x1, x2, x4, x8, x16 lanes 001

(1)

Active

SD/MMC 4/8 100

AS - fast mode 4 001

AS - normal mode 4 011

Avalon-ST

The Avalon-ST configuration scheme is a passive configuration scheme. Avalon-ST is the fastest configuration scheme for Intel

Agilex devices. Avalon-ST configuration supports x8, x16, and x32 modes. The x16 and x32 bit modes use general-purpose

I/Os (GPIOs) for configuration. The x8 bit mode uses dedicated SDM I/O pins.

Note:

The AVST_data[15:0], AVST_data[31:0], AVST_clk, and AVST_valid use dual-purpose GPIOs which operate at

1.2 V. . You can use these pins as regular I/Os after the device enters user mode.

Avalon-ST supports backpressure using the AVST_READY and AVST_VALID pins. Because the time to decompress the

incoming bitstream varies, backpressure support is necessary to transfer data to the Intel Agilex device. For more information

about the Avalon-ST refer to the Avalon Interface Specifications.

JTAG

You can configure the Intel Agilex device using the dedicated JTAG pins. The JTAG port provides seamless access to many

useful tools and functions. In addition to configuring the Intel Agilex, you use the JTAG port for debugging with Signal Tap or

the System Console tools.

(1)

Before you can use CvP you must configure either the periphery image or full image configuration via the AS scheme. Then you can

configure the core image using CvP.

1. Intel

®

Agilex

™

Configuration User Guide

UG-20205 | 2019.10.09

Intel

®

Agilex

™

Configuration User Guide

Send Feedback

6

Loading...

Loading...