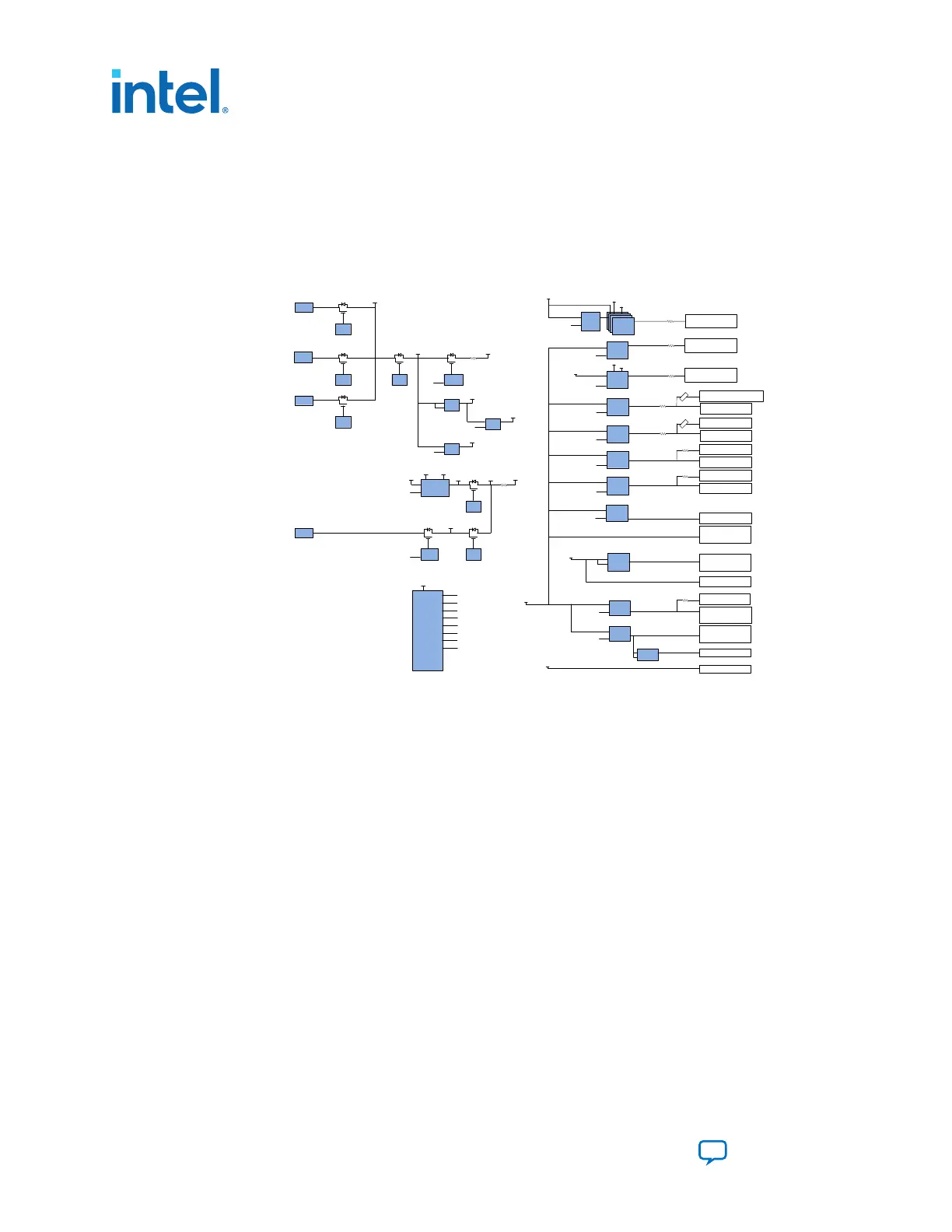

6.9.1. Power Distribution System

The following figure below shows the power distribution system on the A10 FPGA

development board. Regulator efficiencies and sharing are reflected in the currents

shown, which are at conservative absolute maximum levels.

Figure 35. Power Distribution System Block Diagram (ES Edition)

12V

DC_INPUT

J13

LTC4357

U55

LTC4357

U54

ISL6115

U56

12V_MAIN

EN_12V

12V_PCIE

J22

LT4357

U50

12V_ATX

J4

12V_OUT

LTC4352

D43

3.3V_PCIE

J22

ED8101 +

ET4040

U82, U83

LTC4352

D42

LTC4365-1

U52

12V

A10_ VCC_LOW

A10GX VCC, VCCP, VCCHIP,

VCCHSSI

A10_ VCCRAM

A10GX VCCRAM

A10_ VCCRT_GXB

A10GX VCCRT_GXB(L,R)

EC7401

Multiphase

controller

U34

ET4040

U3, U18,

U30, U11

EN63A0

U10

ED8101 +

ET4040

U33,

U90

EN63A0

U31

EN6360

U24

EN6347

U20

EN6347

U23

EN6360

U9

1.1V

16.67A

1.8V

10.23

1.5V

4.7A

0.95V

105 .06A

12V

12V

0.95

5.12A

A10_ 1.8V

A10GX VCCA_PLL, VCCH_GXB(L,R)

A10_ VCCPT

A10GX VCCBAT

BEAD

3.13A

A10_ VCCIO_ MEM

A10GX VCCIO_EMI

MEM_VDDQ

EMI_VDDQ

BEAD

1.5A

1.5V

3.5A

A10_ VCCIO_ FMCA

A10GX VCCIO (FMCA)

FMCA_VADJ

FMCA VADJ

1.5A

1.5V

3.5A

A10_ VCCIO_ FMCB

A10GX VCCIO (FMCB)

FMCB_VADJ

FMCB VADJ

1.5A

1.5V

4.5A

MEM_VDD

EMI VDD

3.3 V

FMCA, FMCB, CLK cleaner,

EZ-USB, DP, SFP+, QSFP,

SDI, level translator

10.87A

LT3082

U36

5.0 V

Char LCD, MAX3378, ADC,

EC7401

5.0V

0.07A

12V

FMCA, FMCB, FAN

EN6337

U57

A10_ VCCIO_ 1.8V

A10GX VCCIO, VCCPGM

EN6337

U51

2.5V

2.31A

1.8 V

EPM2210, EPM570, EPCL,

Flash , Oscillators, Level

shifters VADJ

2.5 V

MEMVEXT, ENET VDD,

EPM2210, VCCIO1, EMP570,

VCCINT, Oscillators

1.5A

1.8V

2.08A

3.3V

1.26A

3.3V

1.94A

LTC3025

U25

ENET_DVDD

1.0V

0.21A

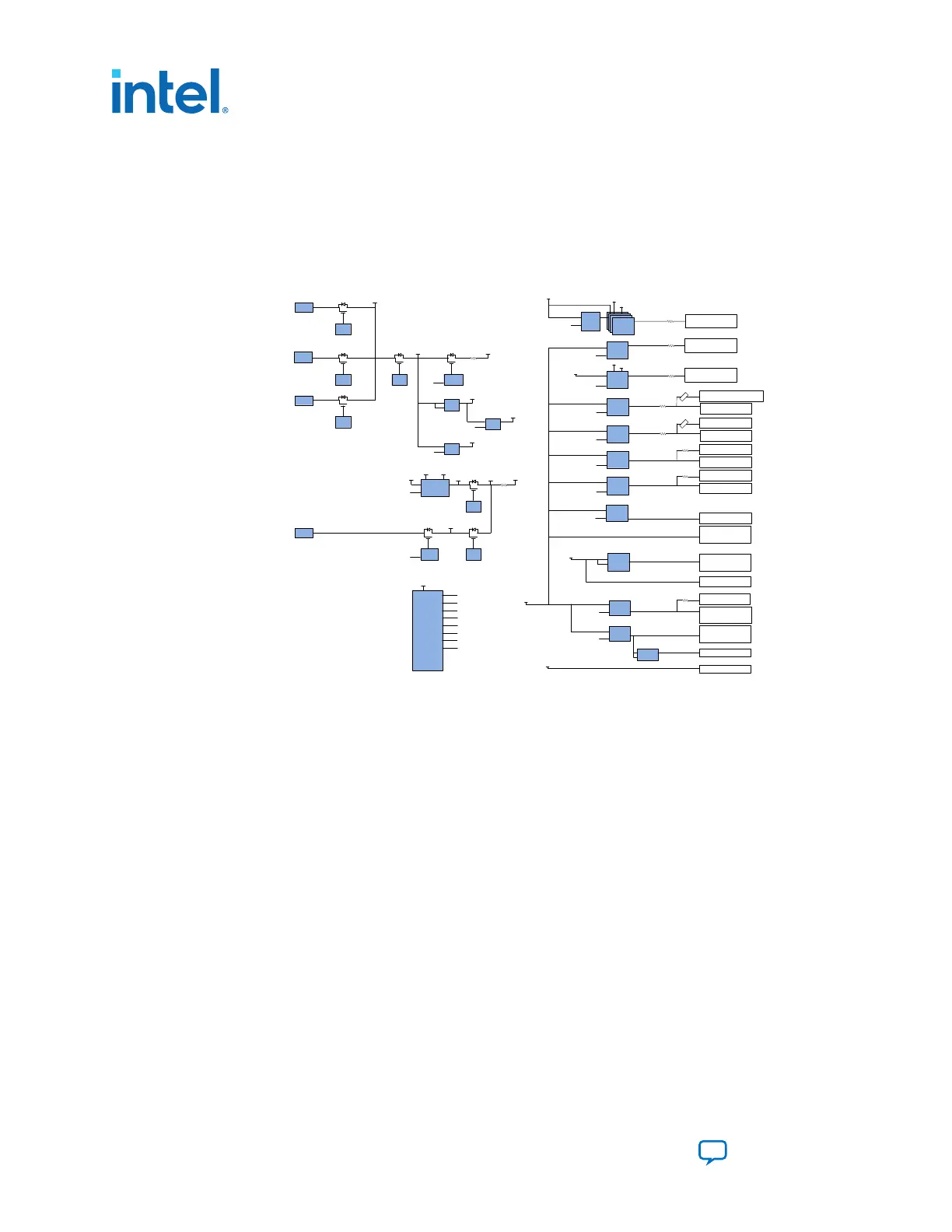

EN_POWER_SEQ

3.3V_LDO

LT1965

U84

3.3V_MUX

3.3V

3.3V_LDO 1.8V_LDO

R408

.00025

R811

.003

R823

.00025

R850

.00025

R879

.003

R862

.003

R871

.003

R95

.003

12V

3.3V

3.3V_LDO

1.8V_LDO

ENET_DVDD

1.8V_LDO

EN_POWER_SEQ

LTC4365-1

U87

EN_3.3V_LDO

LT1965

U19

5V_SEQ

LTM2977

U81

5V_SEQ

EN1

EN2

EN3

EN4

EN5

EN6

EN7

EN8

EN_3.3V_LDO

EN_1.8V_LDO

EN_POWER_SEQ

CNTL0

CNTL1

POWER_EN

(On Switch)

LT_PGM_HEADER

EN_A10_VCC

EN_A10_GROUP2

EN_A10_1.8V

EN_A10_VCCIO

EN_A10_VCC

EN_A10_GROUP2

EN_A10_GROUP2

EN_A10_1.8V

EN_A10_VCCIO

EN_A10_VCCIO

EN_A10_VCCIO

EN_A10_VCCIO

EN_A10_VCCIO

EN_A10_VCCIO

12V

EN12V

Power UP Sequencing:

1) EN_3.3V_LDO

2) EN_1.8V_LDO

3) EN_12V

4) EN_POWER_SEQ

5) EN_A10_VCC

6) EN_A10_GROUP2

7) EN_A10_1.8V

8) EN_A10_VCCIO

Power DOWN Sequencing :

1) DISABLE A10_VCCIO

2) DISABLE A10_1.8V

3) DISABLE A10_GROUP2

4) DISABLE A10_VCC

5) DISABLE POWER_SEQ

6) DISABLE 12V

7) DISABLE 1.8V_LDO

8) DISABLE 3.3V_LDO

PCIe Component Height Restrictions :

-Top Side (Max): 14.47mm

-Bottom Side (Max) 2.67mm

3.3V_LDO

1.8V_LDO

12V

3.3V

A10_VCC

A10_VCCR

A10_VCCPT

A10_VCCIO_1.8V

IN1

IN2

IN3

IN4

IN5

IN6

IN7

IN8

U13

U27

U22

Q2

U17

U35

U88

U39

12V

2.09A

U86

3.3V_PCIE_MUX

1.63A

1.69A

6.20A

2.37A

1.77A

1.77A

2.27A

3.20A

30.08A

9.24A

11.05A

12V

3.3V_LDO

1.8V_LDO

2.12A

13.05A

R316

.003

R165

.00025

3.3V_OUT

1.8V_LDO

LT1965

U85

EN_1.8V_LDO

6. Board Components

683526 | 2023.07.12

Intel

®

Arria

®

10 FPGA Development Kit User Guide

Send Feedback

106

Loading...

Loading...