6.6. Clock Circuitry

6.6.1. On-Board Oscillators

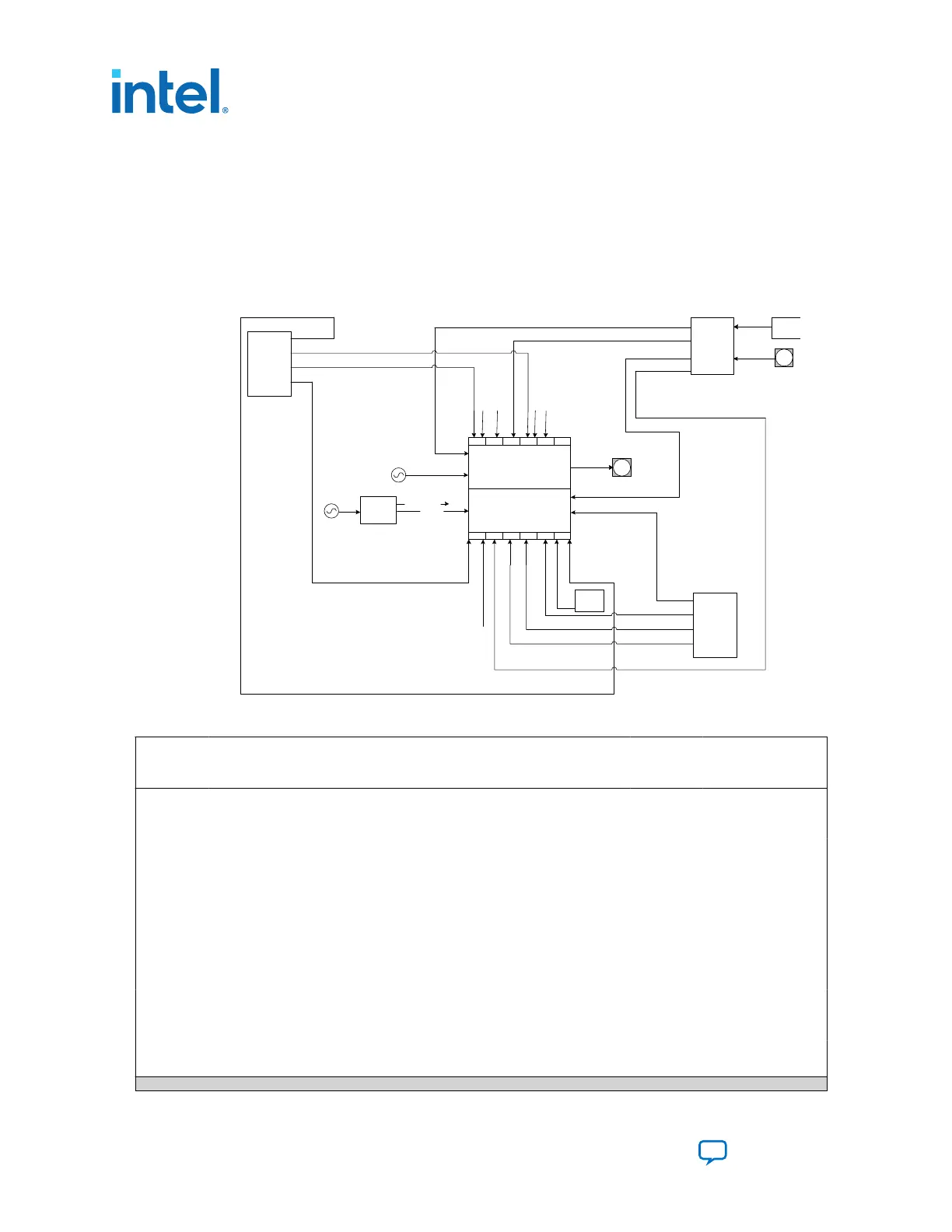

Figure 32. Arria 10 GX FPGA Kit Board Clock Inputs and Default Frequencies

B 2A

B 3A

B 2L

B 3H

1C 1D 1E 1F 1G 1H

4D 4E 4F 4G 4H 4I

Bank 3

Bank 2

Si

5338

CLK 0

CLK 1

CLK 2

CLK 3

SL 18860

Buffer

CLK _50

MV _CLK _50

125 M

Buffer 2: 6

Si 53301 /

Si 53311

100 MHz

Default

100 M_P /N

REFCLK 4_P /N

SMA

50M

PCIE _OB _REFCLK _P /N

PCIE _EDGE _REFCLK _P /N

REFCLK _DP _P /N

REFCLK _SFP _P /N

REFCLK _QSFP _P /N

REFCLK _SDI _P /N

REFCLK _FMCA _P /N

REFCLK _FMCB _P /N

REFCLK _SMA _P/N

CLK _125 M_P /N

Si 5338

CLK 0

CLK 1

CLK 2

CLK 3

CLK _EMI _P /N

133 .33MHz

644 .53125 MHz

644 .53125 MHz

270 MHz

Si 516 /

Si 571

100 MHz

625 MHz

625 MHz

348 MHz

Si570

FMCA _GBTCLK _M2C _P 0/N0

FMCA _GBTCLK _M2C _P 1/N1

FMCB _GBTCLK _M2C_P 0/N0

FMCB _GBTCLK _M2C_P 1/N1

REFCLK 1_P /N

CLK _FPGA _B3_P /N

REFCLK 1_P /N

CLK _FPGA _B2_P /N

SMA

Arria 10

GX

Table 27. On-Board Oscillators

Source Schematic Signal Name Frequency I/O Standard Arria 10

FPGA Pin

Number

Application

U14

REFCLK_SMA_P

302.083333 MHz 1.8 V LVDS N37 Transceiver

reference clocks

Bank-1H

REFCLK_SMA_N

1.8 V LVDS N38

REFCLK_FMCB_P

625 MHz 1.8 V LVDS AA8 FMC B reference

clocks

REFCLK_FMCB_N

1.8 V LVDS AA7

REFCLK_FMCA_P

625 MHz 1.8 V LVDS AN8 FMC A reference

clocks

REFCLK_FMCA_N

1.8 V LVDS AN7

PCIE_OB_REFCLK_P

100 MHz 1.8 V LVDS AN37 PCIE reference

clocks

PCIE_OB_REFCLK_N

1.8 V LVDS AN38

U26

CLK_EMI_P

133.33 MHz 1.8 V LVDS F34 EMI reference

clocks

CLK_EMI_N

1.8 V LVDS F35

REFCLK_QSFP_P

644.53125 MHz 1.8 V LVDS R37 QSFP reference

clocks

continued...

6. Board Components

683526 | 2023.07.12

Intel

®

Arria

®

10 FPGA Development Kit User Guide

Send Feedback

74

Loading...

Loading...