3 Testing 16860 Performance

60 Keysight 16860 Series Portable Logic Analyzer Service Guide

16 Wait for logic analyzer to complete 100 acquisitions at the new pulse generator frequency

without displaying any error. If an error is displayed, decrease the pulse generator frequency by 1

MHz and then again wait for 100 acquisitions at this new frequency without any error. Repeat this

step until you get 100 acquisitions without any error display.

17 Click the Stop toolbar button to stop the data acquisition.

18 Note the generator frequency setting. This will be used in the next section to verify the data rate.

Pod 4 Clock - Setup for Maximum Data Rate

1 Verify that the Generator is set to the frequency found in the last section as a starting point.

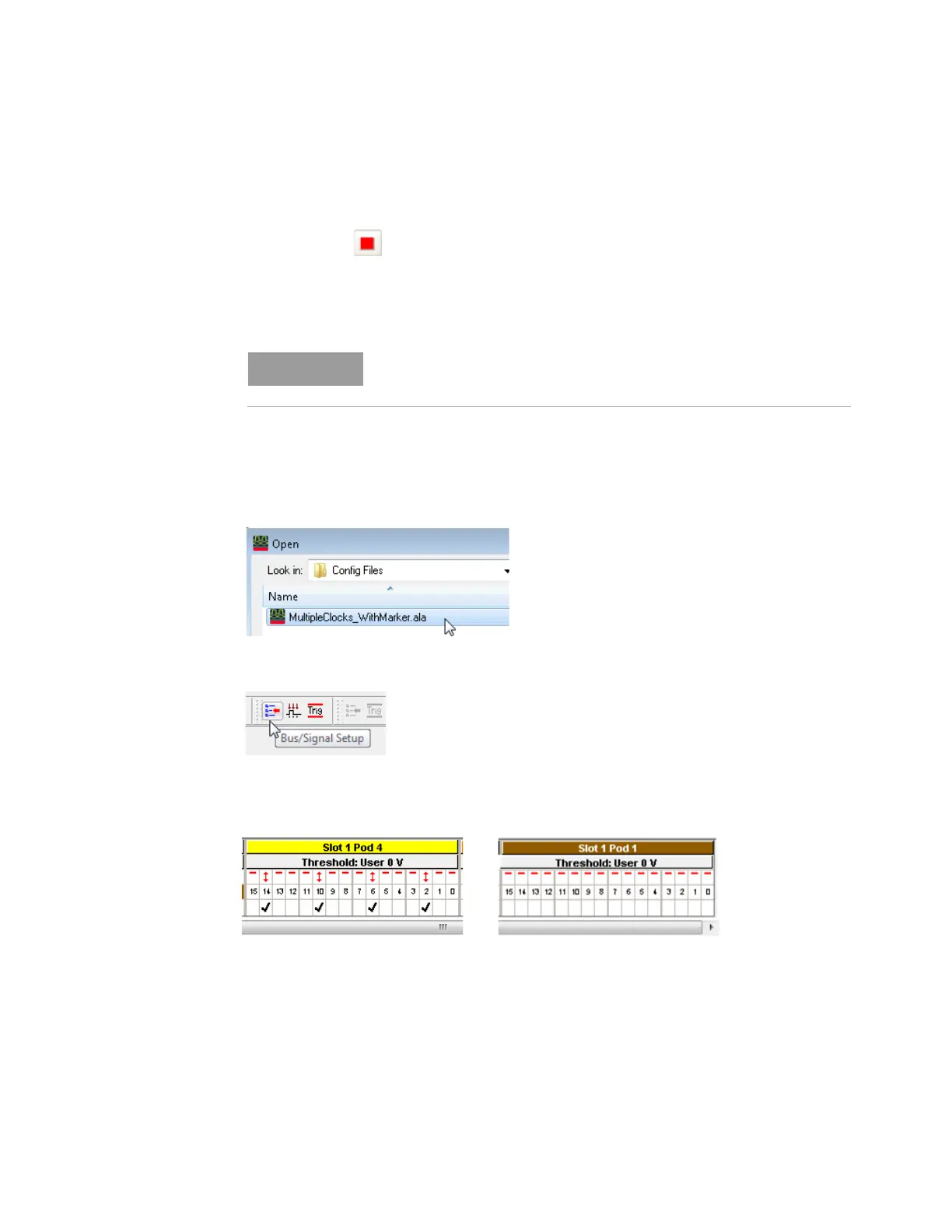

2Load the MultipleClocks_WithMarker.ala configuration file. If asked to save the current

configuration file, click No.

3Open the Bus/Signal Setup dialog by clicking the Setup Icon in the tool bar.

4 Unassign the data bits from Pod1.

5 Assign bits 2, 6, 10, and 14 of Pod 4.

6Open the Sampling tab.

7 In the clock assignment area, set Pod 1 Clock to Don't Care and set Pod 4 Clock to Both Edges.

This section is only applicable to models: 16862A, 16863A & 16864A.

Loading...

Loading...