3 Testing 16860 Performance

74 Keysight 16860 Series Portable Logic Analyzer Service Guide

• Bits 2 & 10 to Channel 2 Output

• Bits 6 & 14 to Channel 2 Output (not)

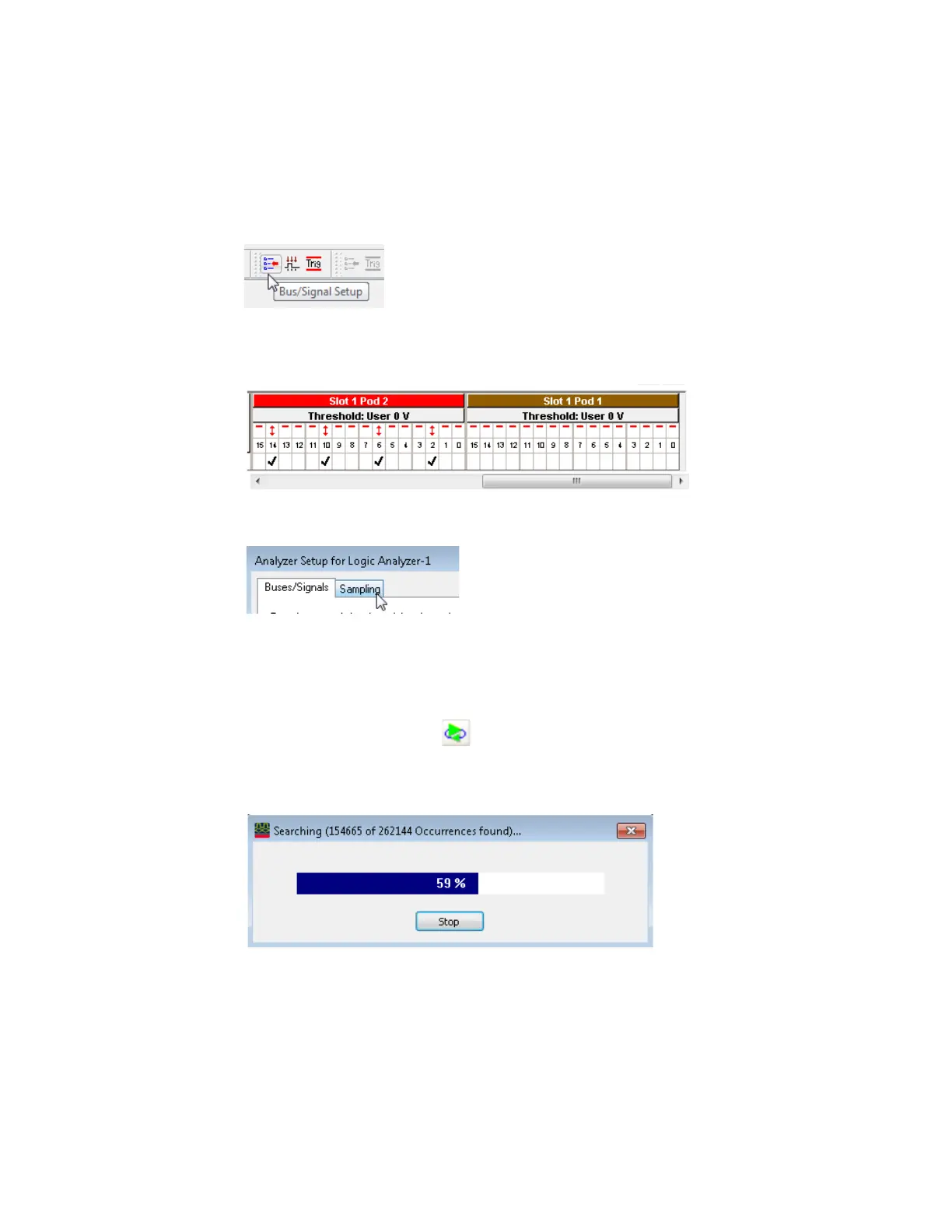

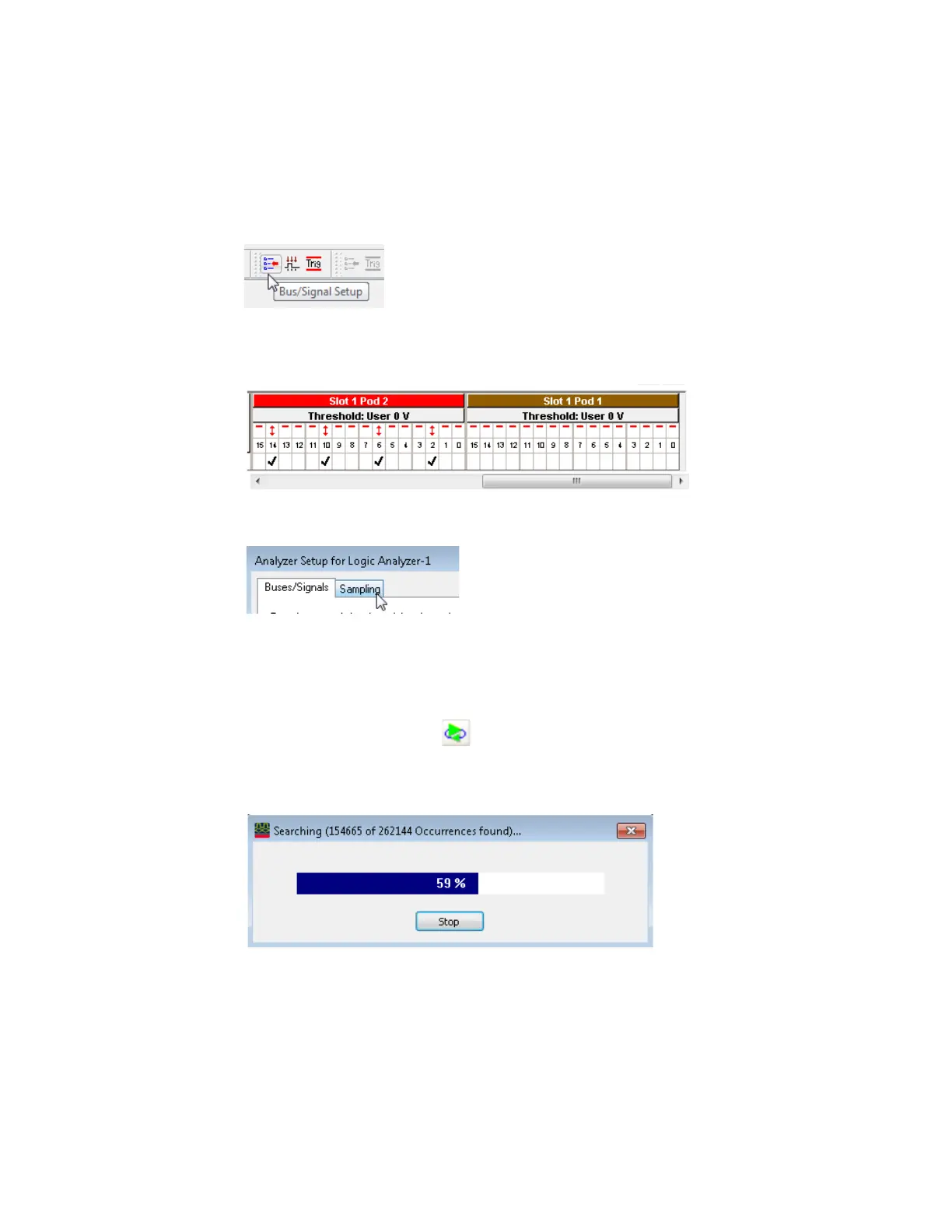

4Open the Bus/Signal Setup dialog by clicking the Setup Icon in the toolbar.

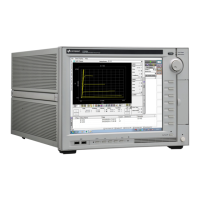

5 Unassign the data bits from Pod1.

6 Assign bits 2, 6, 10, and 14 of Pod 2.

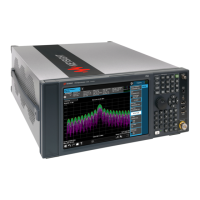

7Open the Sampling tab.

8 Adjust the sample position using the procedure described earlier by clicking the Eye Scan: Sample

Position and Thresholds button. Select the eye closest to -1 ns.

9 Close the dialog windows by clicking OK.

Single Clock Both Edges - Pod 2 Data - Measuring Maximum Data Rate

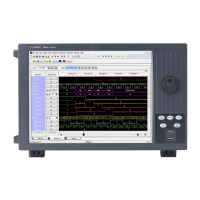

1 Select the Run Repetitive icon . Let the logic analyzer run for about 1 minute. The analyzer will

acquire data and the Listing Window will continuously update. A marker search window will

appear and show progress.

2 If incorrect data is found, the following window appears. The data in the listing window should be

A's & 5's.

Loading...

Loading...