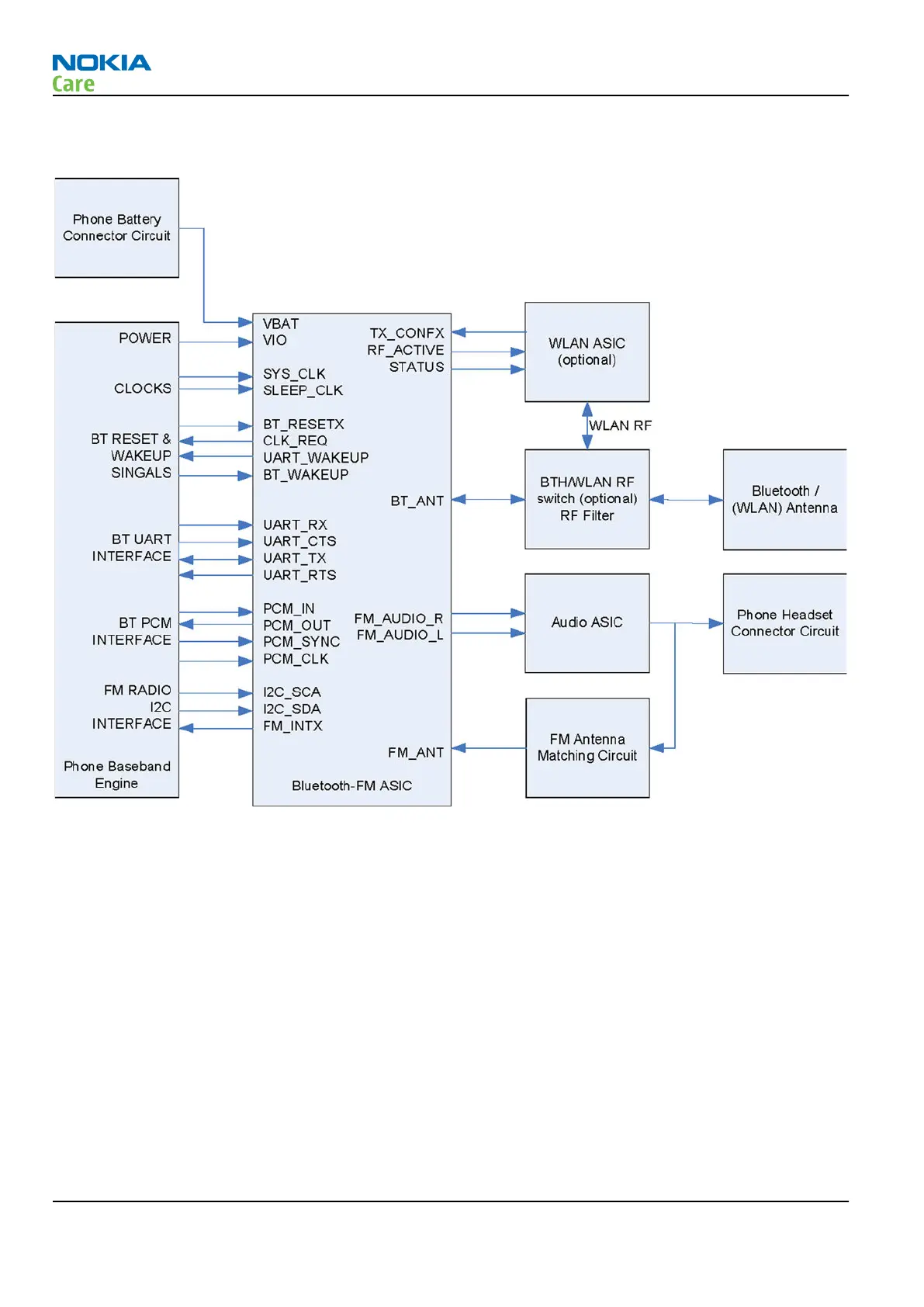

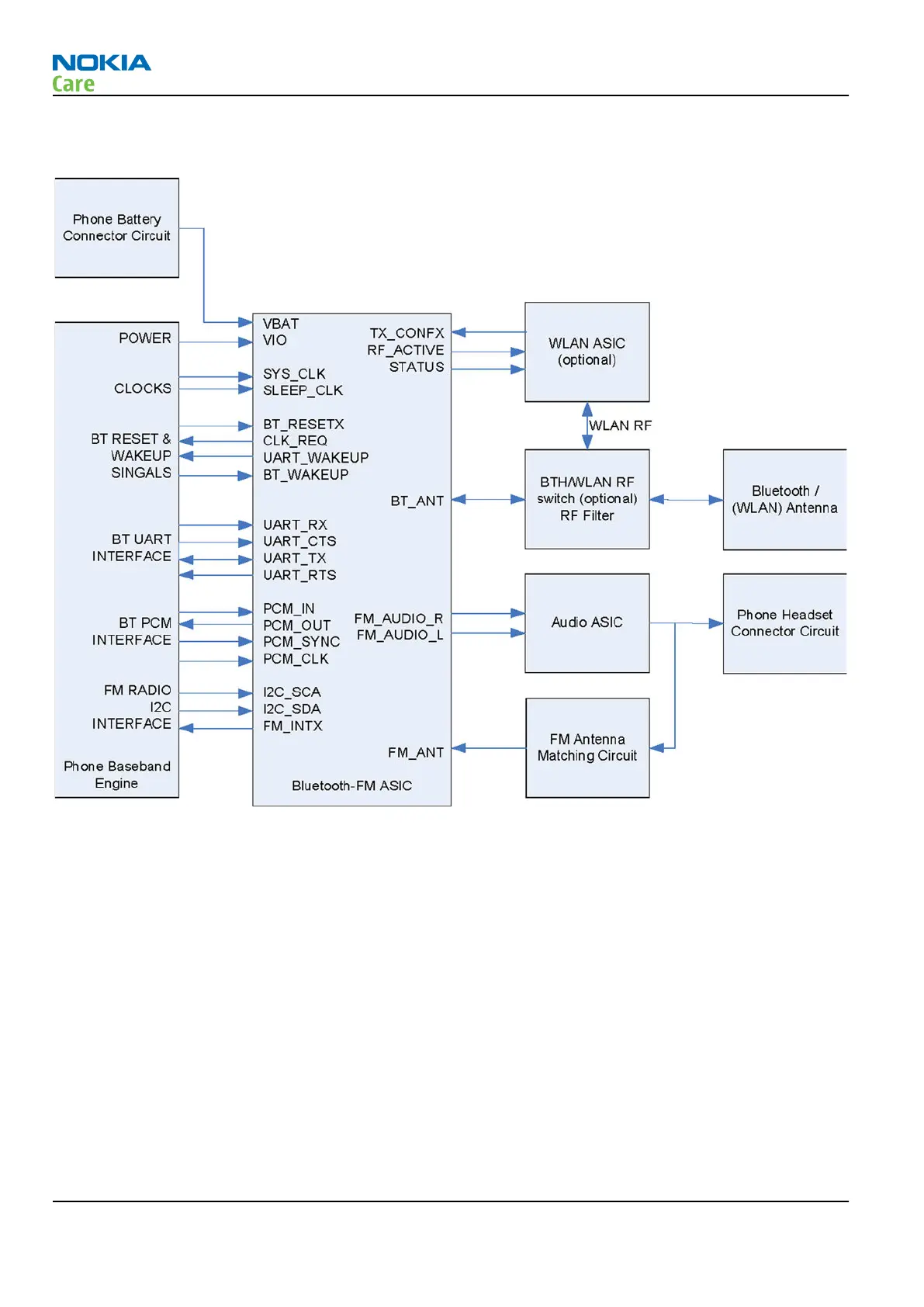

Bluetooth and FM radio block diagram

Figure 47 Bluetooth and FM radio block diagram

WLAN

WLAN engine is divided into STLC4560 WLAN transceiver module and radio front-end module (FEM) RF5924.

STMicroelectronics Phaser STLC4560 is a three-die multichip module, partitioned to radio, baseband and

energy management die. STLC4560 is packaged to 8.5 mm x 8.0 mm x 1.4 mm 240-ball 0.5 mm pitch LFBGA.

STLC4560 implements 802.11b/g WLAN radio for embedded, low-power and small form factor mobile

applications. STLC4560 conforms to the IEEE 802.11b/g protocols operating in 2.4 GHz band supporting OFDM

data rates of 54, 48, 36, 24, 18, 12, 9, and 6 Mbps as well as CCK data rates of 11 and 5.5 Mbps and legacy

data rates of 2 and 1 Mbps. IEEE802.11e/i protocol extensions are included to implement quality of service

(QoS) and security functions.

STLC4560 has a fully integrated radio chip including a direct-conversion transceiver, RF synthesizer and VCO,

and high-speed data converters. Digital interface is used for transferring the sampled data between radio

and baseband chip. The baseband chip implements OFDM/CCK digital baseband processor and ARM9- based

MAC with internal SRAM memories. The baseband includes required logic and interfaces to enable time-shared

simultaneous use of BT and WLAN.

RM-247

System Module

Page 7 –14 COMPANY CONFIDENTIAL Issue 1

Copyright © 2008 Nokia. All rights reserved.

Loading...

Loading...