Miscellaneous Interfaces

NVIDIA Jetson Xavier NX DG-09693-001_v1.7 | 73

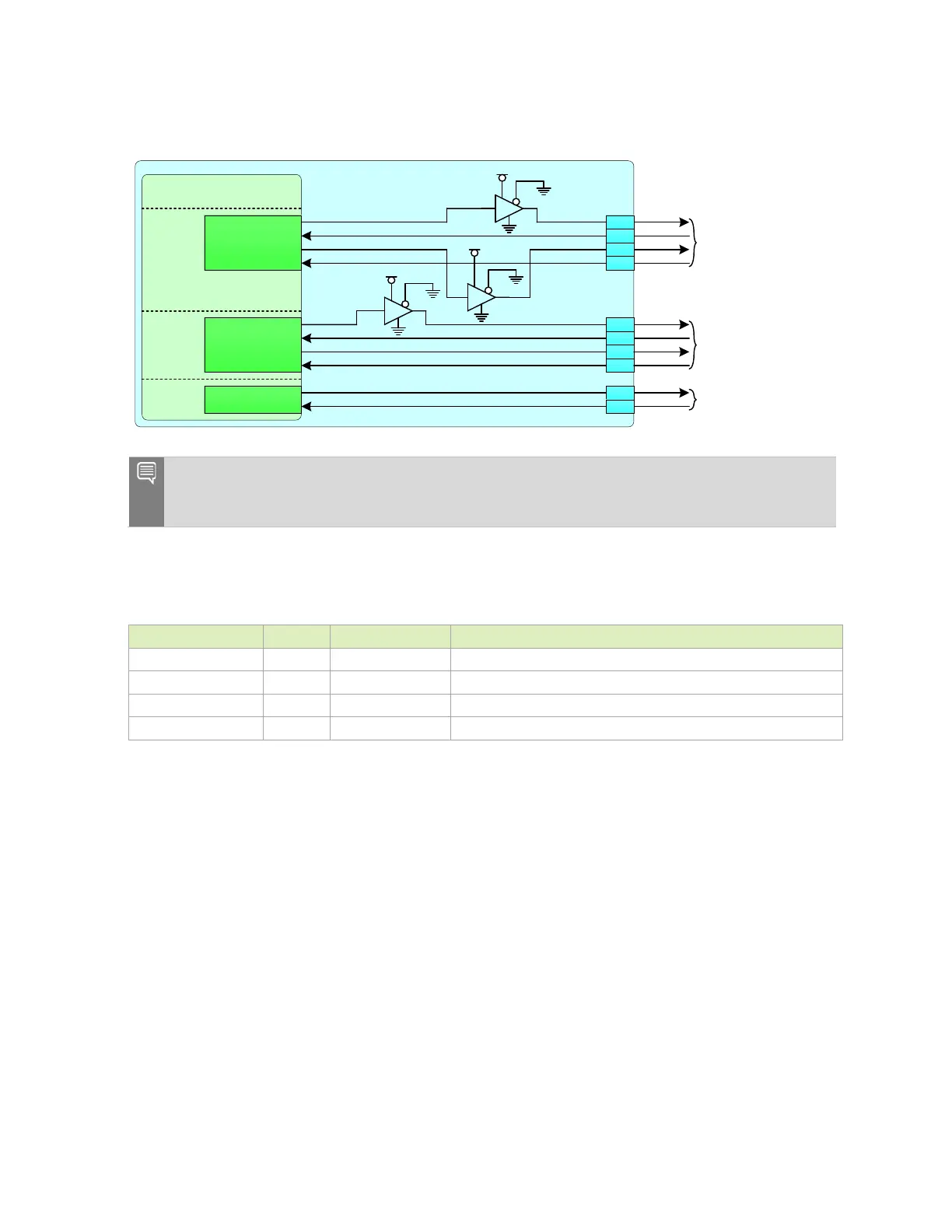

Figure 12-5. UART Connections

Jetson

SoC – UART

UART1_TX

UART1_RX

UART1_RTS_N

UART 1_CTS_N

CAM

D ebu g UA RT

UART0_TXD

UART0_RXD

UART0_RTS*

UART0_CTS*

UART1_TXD

UART1_RXD

UART1_RTS*

UART1_CTS*

UART2_TXD

UART2_RXD

UART3_TX

UART3_RX

AO

UART2_TX

UART2_RX

UART2_RTS_N

UART 2_CTS_N

UART

205

203

236

238

101

99

103

105

207

209

UART general

UART general (i.e.

M. 2 Key E)

GND

OE*

VCC

GND

OE*

VCC

GND

OE*

VCC

1.8V

1.8V

1.8V

Note: The buffers on UART0_TXD, UART0_RTS* and UART1_TXD are there to prevent

connected devices from changing the pin state during power-on. These pins are associated

with SoC Strapping pins.

Table 12-8. UART Signal Connections

Ball Name Type Termination Description

UART[2:0]_TXD O UART Transmit: Connect to peripheral RXD pin of device

UART[2:0]_RXD I UART Receive: Connect to peripheral TXD pin of device

UART[1:0]_CTS* I UART Clear to Send: Connect to peripheral RTS pin of device

UART[1:0]_RTS* O UART Request to Send: Connect to peripheral CTS pin of device

Loading...

Loading...