Miscellaneous Interfaces

NVIDIA Jetson Xavier NX DG-09693-001_v1.7 | 72

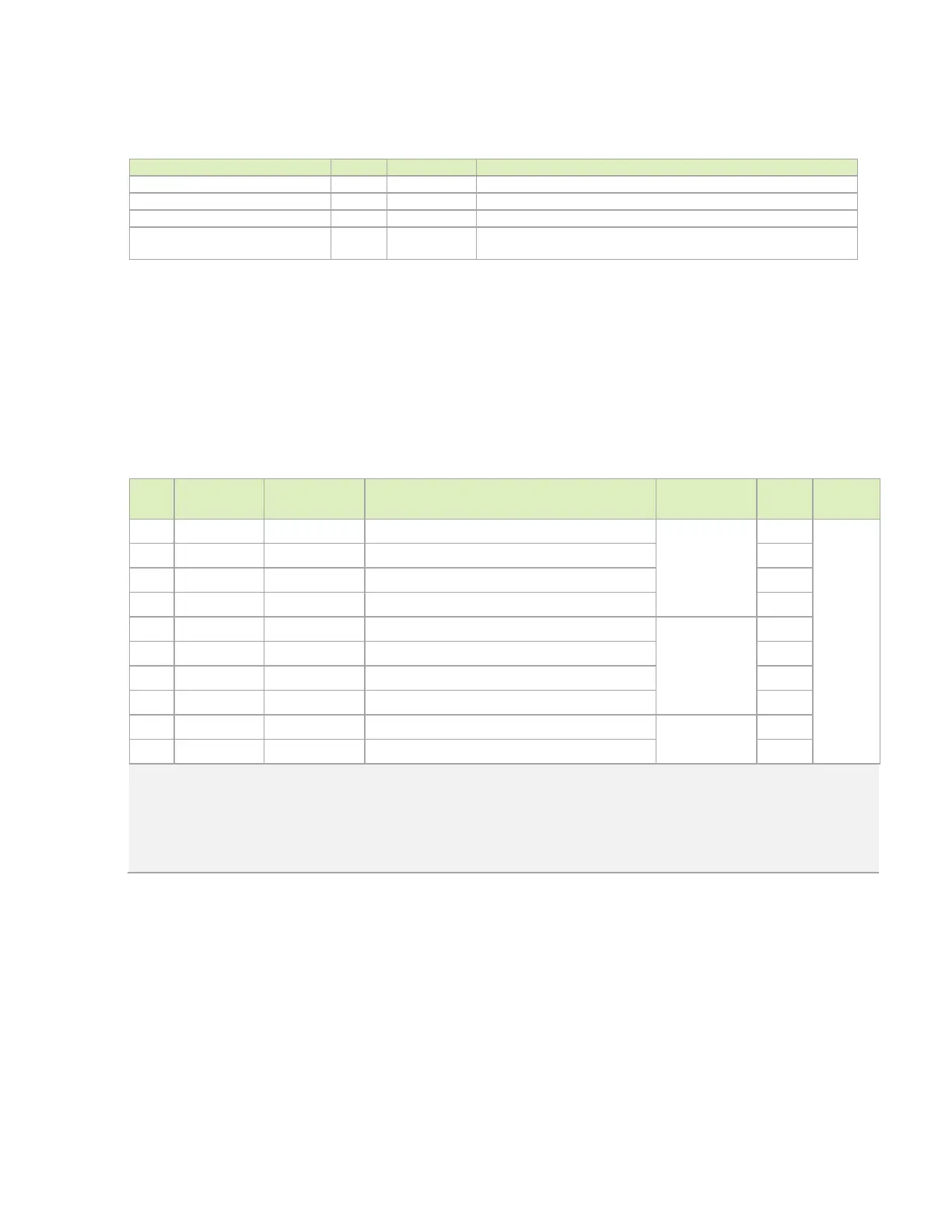

Table 12-6. SPI Signal Connections

Module Pin Names (Function)

SPI Clock.: Connect to peripheral CLK pin(s)

SPI Data Output: Connect to target peripheral MOSI pin(s)

SPI Data Input: Connect to target peripheral MISO pin(s)

SPI Chip Selects.: Connect one CSx* pin per SPI interface to

each target peripheral CS pin on the interface

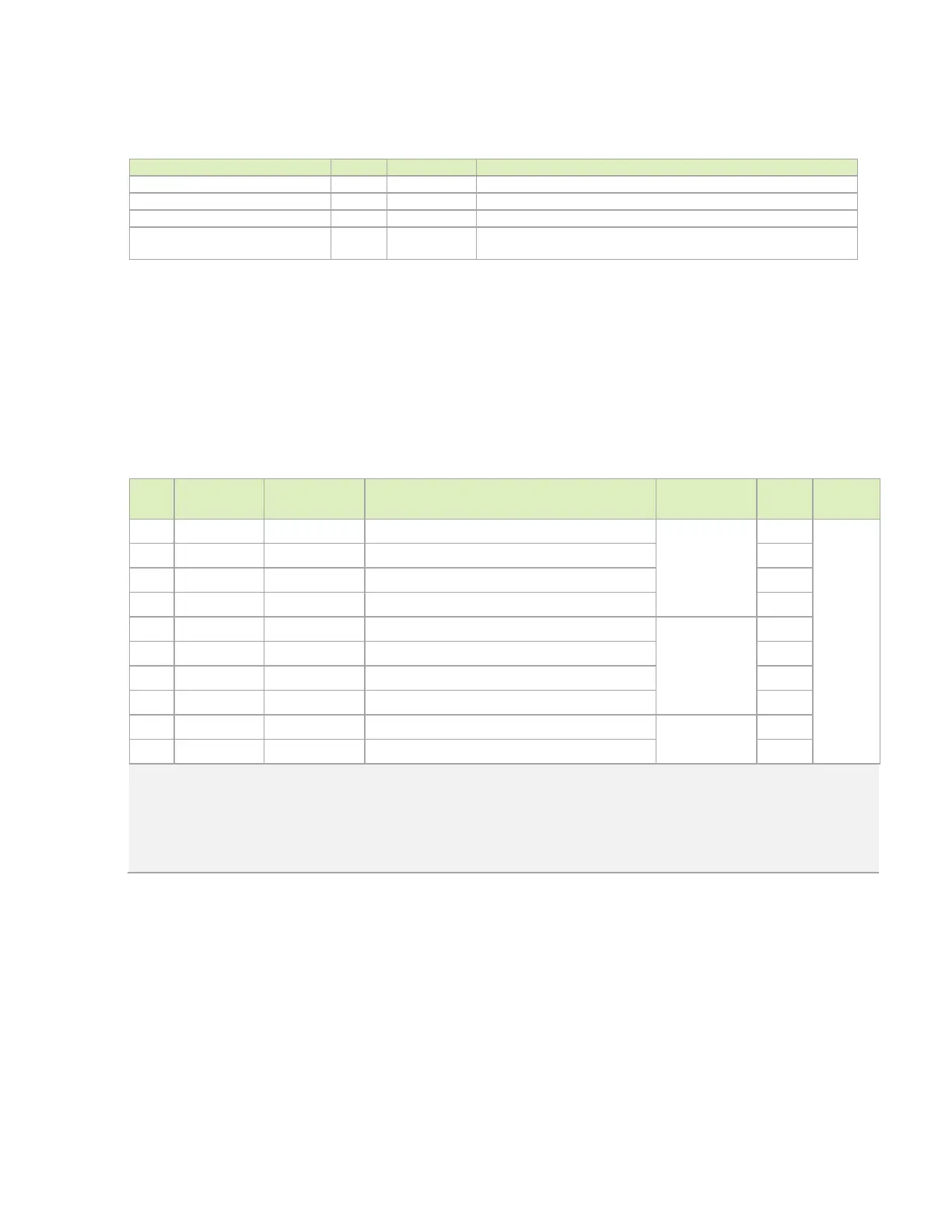

12.3 UART

The Jetson Xavier NX brings three UARTs out to the main connector. See Figure 12-5 for

typical assignments of the three available UARTs.

Table 12-7. UART Pin Descriptions

Pin #

Module Pin

Name

Xavier Signal Usage/Description

Recommended

Usage

Directio

n

Pin Type

99 UART0_TXD UART2_TX UART 0 Transmit

UART general

(i.e. M.2 Key E)

Output

CMOS –

1.8V

101 UART0_RXD UART2_RX UART 0 Receive Input

103 UART0_RTS* UART2_RTS UART 0 Request to Send Output

105 UART0_CTS* UART2_CTS UART 0 Clear to Send Input

203 UART1_TXD UART1_TX UART 1 Transmit

UART general

Output

205 UART1_RXD UART1_RX UART 1 Receive Input

207 UART1_RTS* UART1_RTS UART 1 Request to Send Output

209 UART1_CTS* UART1_CTS UART 1 Clear to Send Input

236 UART2_TXD UART3_TX UART 2 Transmit.

Debug UART

Output

238 UART2_RXD UART3_RX UART 2 Receive Input

Notes:

1. In the Type/Dir column, Output is from Jetson Xavier NX. Input is to Jetson Xavier NX. Bidir is for Bidirectional signals.

2. The direction indicated for the UART pins except for is true when used for that function. Otherwise, these pins support GPIO

functionality and most can support both input and output (bidirectional) functionality. The exception is UART0_TXD, UART0_RTS*

and UART1_TXD. These have output-only buffers on the module to keep them from being affected by connected devices during

boot as they are associated with SoC strapping pins.

Loading...

Loading...