430

Index Registers Section 9-17

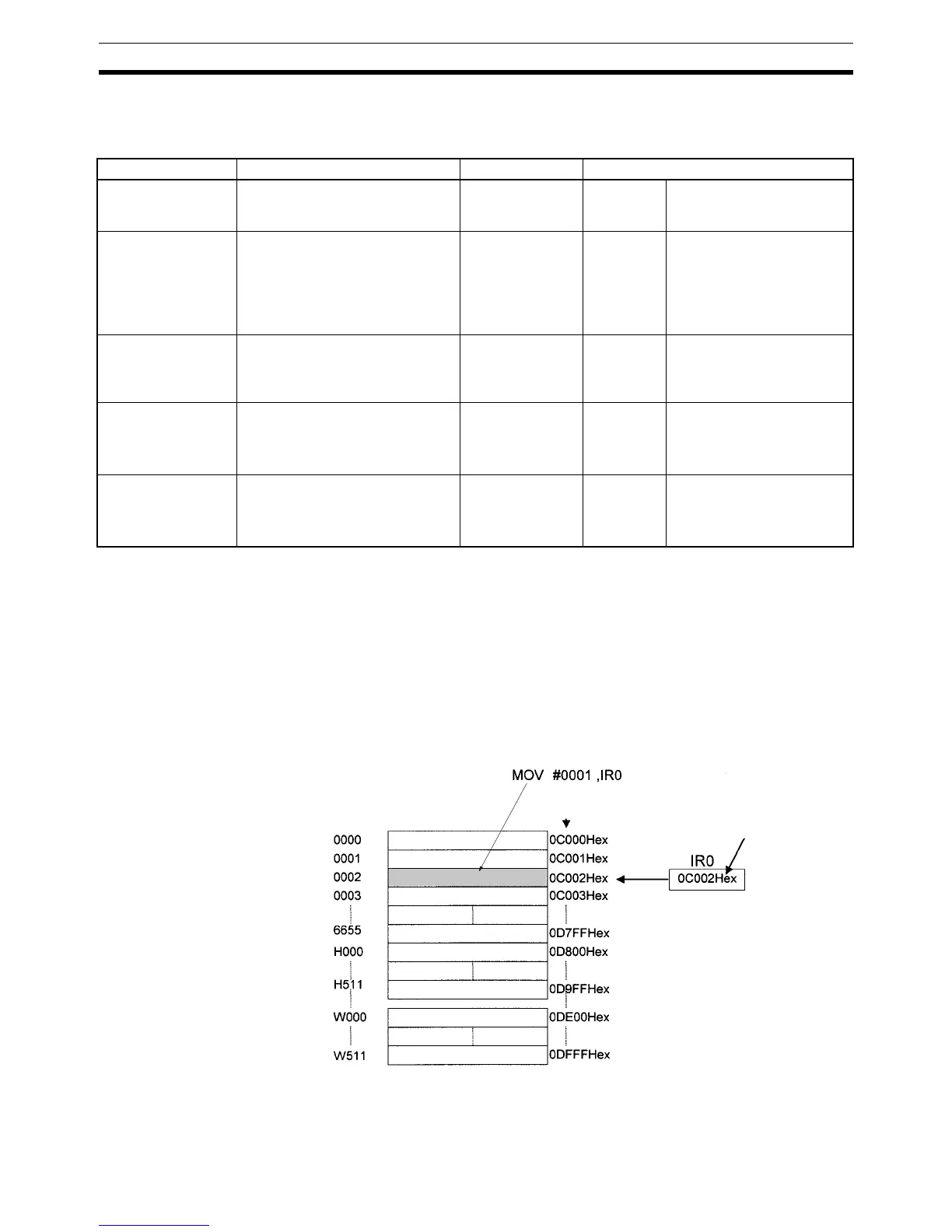

The following table shows the variations available when indirectly addressing

I/O memory with Index Registers. (IR@ represents an Index Register from IR0

to IR15.)

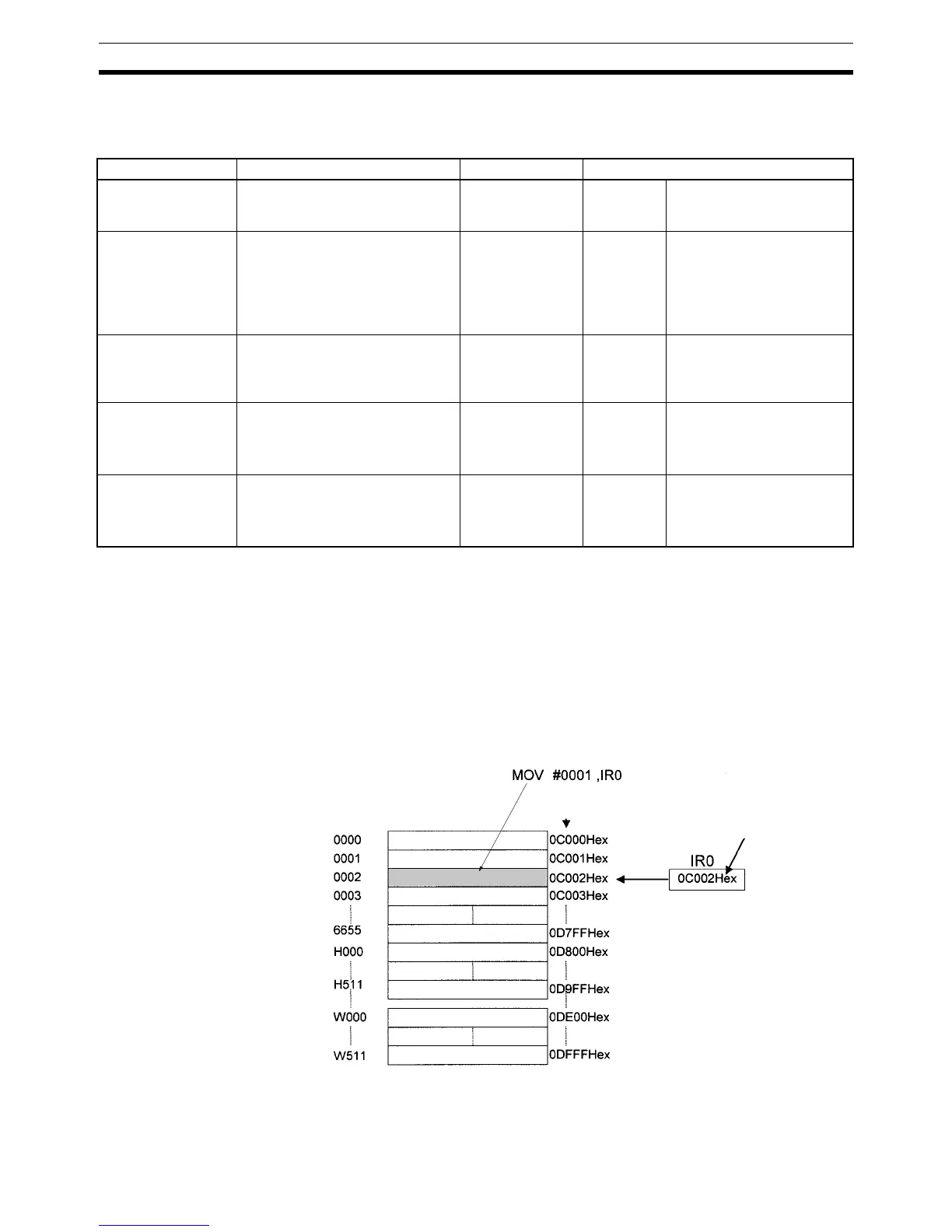

Example This example shows how to store the PLC memory address of a word

(CIO 0002) in an Index Register (IR0), use the Index Register in an instruc-

tion, and use the auto-increment variation.

MOVR(560) 0002 IR0 Stores the PLC memory address of

CIO 0002 in IR0.

MOV(021) #0001 ,IR0 Writes #0001 to the PLC memory ad-

dress contained in IR0.

MOV(021) #0020 +1,IR0 Reads the content of IR0, adds 1,

and writes #0020 to that PLC memo-

ry address.

Note The PLC memory addresses are listed in the diagram above, but it isn’t nec-

essary to know the PLC memory addresses when using Index Registers.

Variation Function Syntax Example

Indirect addressing The content of IR@ is treated as

the PLC memory address of a bit

or word.

,IR@ LD ,IR0 Loads the bit at the PLC

memory address contained

in IR0.

Indirect addressing

with constant offset

The constant prefix is added to the

content of IR@ and the result is

treated as the PLC memory

address of a bit or word.

The constant may be any integer

from –2,048 to 2,047.

Constant ,IR@

(Include a + or –

in the constant.)

LD +5,IR0 Adds 5 to the contents of IR0

and loads the bit at that PLC

memory address.

Indirect addressing

with DR offset

The content of the Data Register

is added to the content of IR@ and

the result is treated as the PLC

memory address of a bit or word.

DR@,IR@ LD

DR0,IR0

Adds the contents of DR0 to

the contents of IR0 and

loads the bit at that PLC

memory address.

Indirect addressing

with auto-increment

After referencing the content of

IR@ as the PLC memory address

of a bit or word, the content is

incremented by 1 or 2.

Increment by 1:

,IR@+

Increment by 2:

,IR@++

LD , IR0++ Loads the bit at the PLC

memory address contained

in IR0 and then increments

the content of IR0 by 2.

Indirect addressing

with auto-decrement

The content of IR@ is decre-

mented by 1 or 2 and the result is

treated as the PLC memory

address of a bit or word.

Decrement by 1:

,–IR@

Decrement by 2:

,– –IR@

LD , – –IR0 Decrements the content of

IR0 by 2 and then loads the

bit at that PLC memory

address.

#0001

#0020

Regular

data area

address

I/O memory

PLC memory

address

MOVE TO REGISTER instruction

MOVR(560) 0002 IR0

Pointer

Loading...

Loading...