488

Instruction Execution Times and Number of Steps Section 10-5

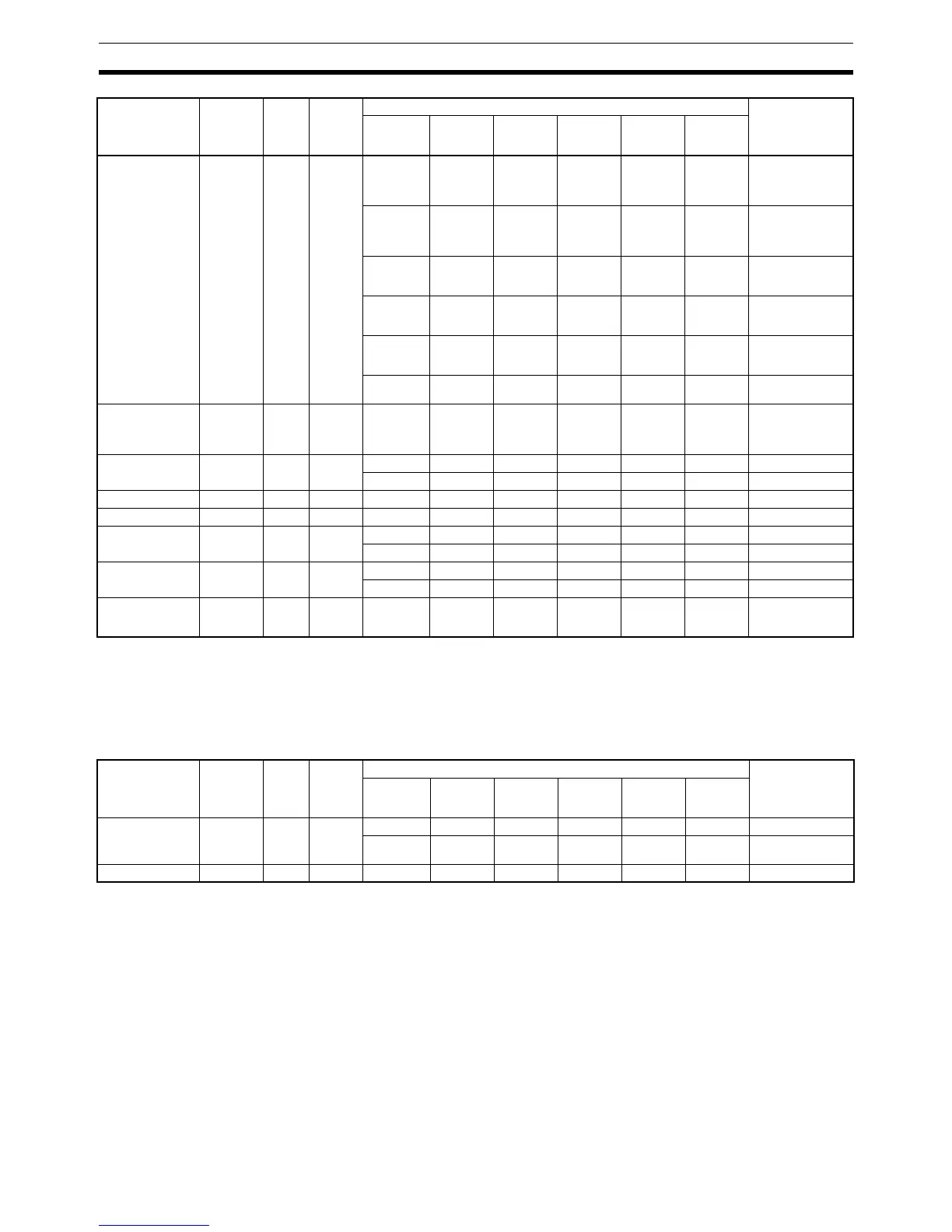

Note 1. When a double-length operand is used, add 1 to the value shown in the

length column in the following table.

2. Supported only by CPU Units Ver. 2.0 or later.

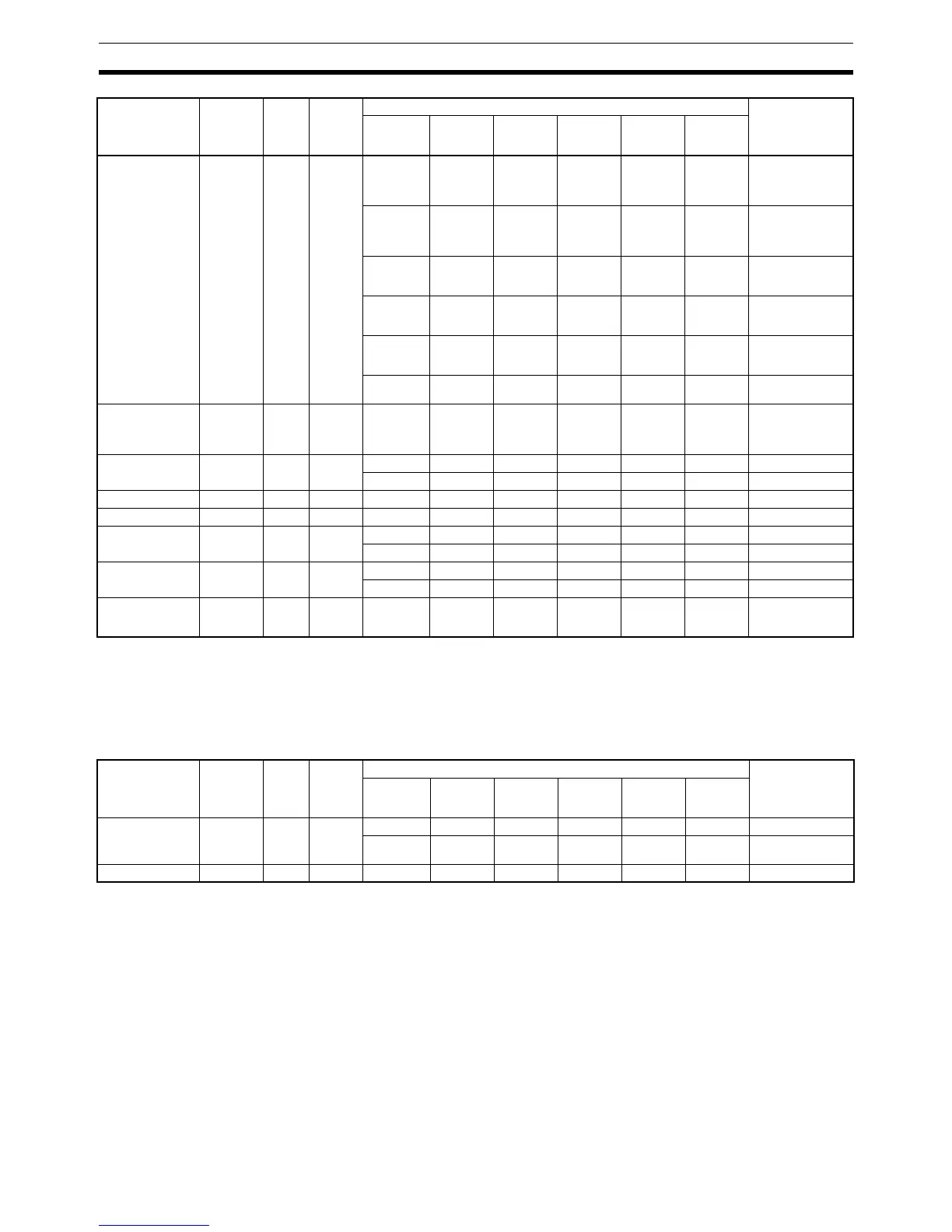

10-5-20 Step Instructions

Note When a double-length operand is used, add 1 to the value shown in the length

column in the following table.

COMPARISON

TABLE LOAD

CTBL 882 4 --- --- --- --- 238.0 235.0 Registering target

value table and

starting comparison

for 1 target value

--- --- --- --- 14.42 ms 9.97 ms Registering target

value table and

starting comparison

for 48 target values

--- --- --- --- 289.0 276.0 Registering range

table and starting

comparison

--- --- --- --- 198.0 183.0 Only registering tar-

get value table for 1

target value

--- --- --- --- 14.40 ms 9.61 ms Only registering tar-

get value table for

48 target values

--- --- --- --- 259.0 239.0 Only registering

range table

COUNTER FRE-

QUENCY CON-

VERT

(See note 2.)

PRV2 883 4 --- --- --- --- 23.03 22.39 ---

SPEED OUTPUT SPED 885 4 --- --- --- --- 56.00 89.3 Continuous mode

--- --- --- --- 62.47 94.9 Independent mode

SET PULSES PULS 886 4 --- --- --- --- 26.20 32.9 ---

PULSE OUTPUT PLS2 887 5 --- --- --- --- 100.80 107.5 ---

ACCELERATION

CONTROL

ACC 888 4 --- --- --- --- 90.80 114.8 Continuous mode

--- --- --- --- 80.00 122.1 Independent mode

ORIGIN SEARCH ORG 889 3 --- --- --- --- 106.13 116.0 Origin search

--- --- --- --- 52.00 102.1 Origin return

PULSE WITH

VARIABLE DUTY

FACTOR

PWM 891 4 --- --- --- --- 25.80 33.0 ---

Instruction Mnemonic Code Length

(steps)

(See

note 1.)

ON execution time (

µs) Conditions

CPU6@H-R CPU6@HCPU4@HCPU4@ CJ1M

excluding

CPU11/21

CJ1M

CPU11/21

Instruction Mnemonic Code Length

(steps)

(See

note.)

ON execution time (

µs) Conditions

CPU6@H-R CPU6@HCPU4@HCPU4@ CJ1M

excluding

CPU11/21

CJ1M

CPU11/21

STEP DEFINE STEP 008 2 17.4 17.4 20.7 27.1 35.9 37.1 Step control bit ON

11.8 11.8 13.7 24.4 13.8 18.3 Step control bit

OFF

STEP START SNXT 009 2 6.6 6.6 7.3 10.0 12.1 14.0 ---

Loading...

Loading...