RL78/G13 CHAPTER 11 A/D CONVERTER

R01UH0146EJ0100 Rev.1.00 488

Sep 22, 2011

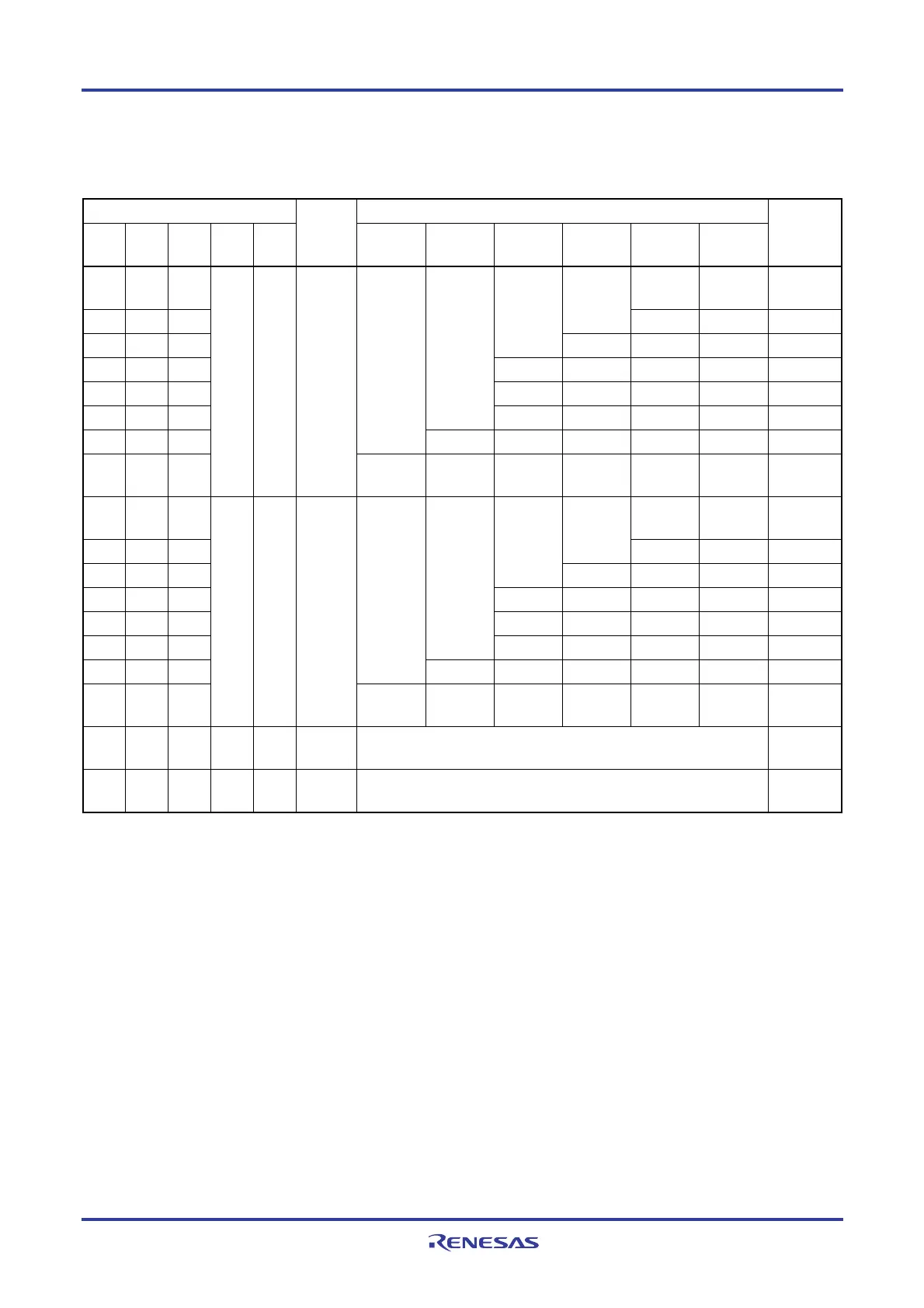

Table 11-3. A/D Conversion Time Selection (5/8)

(5) 3.6 V ≤ V

DD ≤ 5.5 V when there is stabilization wait time (hardware trigger wait mode)

A/D Converter Mode Register 0 (ADM0)

Conversion Time Selection

FR2 FR1 FR0 LV1 LV0

Mode

f

CLK = 1

MHz

fCLK = 2

MHz

fCLK = 4

MHz

fCLK = 8

MHz

fCLK = 16

MHz

fCLK = 32

MHz

Conversion

Clock (f

AD)

0 0 0

Setting

prohibited

54

μ

s

fCLK/64

0 0 1

Setting

prohibited

54

μ

s

27

μ

s fCLK/32

0 1 0

Setting

prohibited

54

μ

s

27

μ

s 13.5

μ

s fCLK/16

0 1 1 54

μ

s

27

μ

s 13.5

μ

s 6.75

μ

s fCLK/8

1 0 0 40.5

μ

s

20.25

μ

s 10.125

μ

s 5.0625

μ

s fCLK/6

1 0 1

Setting

prohibited

33.75

μ

s

16.875

μ

s 8.4375

μ

s 4.2188

μ

s fCLK/5

1 1 0

Setting

prohibited

54

μ

s

27

μ

s 13.5

μ

s 6.75

μ

s 3.375

μ

s fCLK/4

1 1 1

0 0 Normal 1

54

μ

s

27

μ

s 13.5

μ

s 6.75

μ

s 3.375

μ

s

Setting

prohibited

fCLK/2

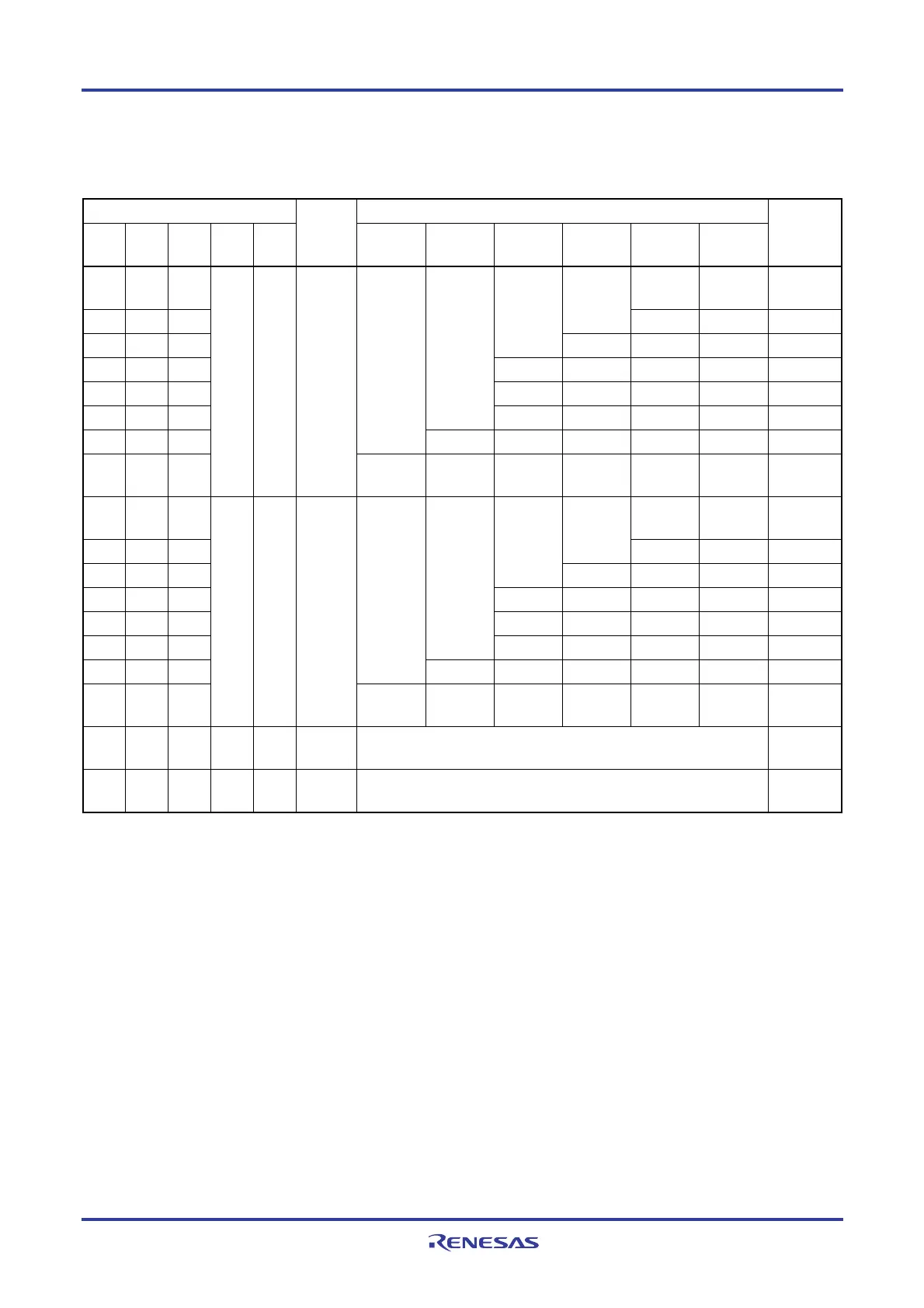

0 0 0

Setting

prohibited

50

μ

s fCLK/64

0 0 1

Setting

prohibited

50

μ

s 25

μ

s fCLK/32

0 1 0

Setting

prohibited

50

μ

s 25

μ

s 12.5

μ

s fCLK/16

0 1 1 50

μ

s 25

μ

s 12.5

μ

s 6.25

μ

s fCLK/8

1 0 0 37.5

μ

s 18.75

μ

s 9.375

μ

s 4.6875

μ

s fCLK/6

1 0 1

Setting

prohibited

31.25

μ

s 15.625

μ

s 7.8125

μ

s 3.90625

μ

sfCLK/5

1 1 0

Setting

prohibited

50

μ

s 25

μ

s 12.5

μ

s 6.25

μ

s 3.125

μ

s fCLK/4

1 1 1

0 1 Normal 2

50

μ

s 25

μ

s 12.5

μ

s 6.25

μ

s 3.125

μ

s

Setting

prohibited

f

CLK/2

× × ×

1 0

Low-

voltage 1

Setting prohibited

−

× × ×

1 1

Low-

voltage 2

Setting prohibited

−

Cautions 1. When rewriting the FR2 to FR0, LV1, and LV0 bits to other than the same data, stop A/D conversion

once (ADCS = 0) beforehand.

2. The above conversion time does not include clock frequency errors. Select conversion time, taking

clock frequency errors into consideration.

3. While in the hardware trigger wait mode, the conversion time includes the time spent waiting for

stabilization after the hardware trigger is detected.

Remark f

CLK: CPU/peripheral hardware clock frequency

Loading...

Loading...