MicroBlaze Processor Reference Guide 260

UG984 (v2018.2) June 21, 2018 www.xilinx.com

Chapter 5: MicroBlaze Instruction Set Architecture

mul

Multiply

mul

rD, rA, rB

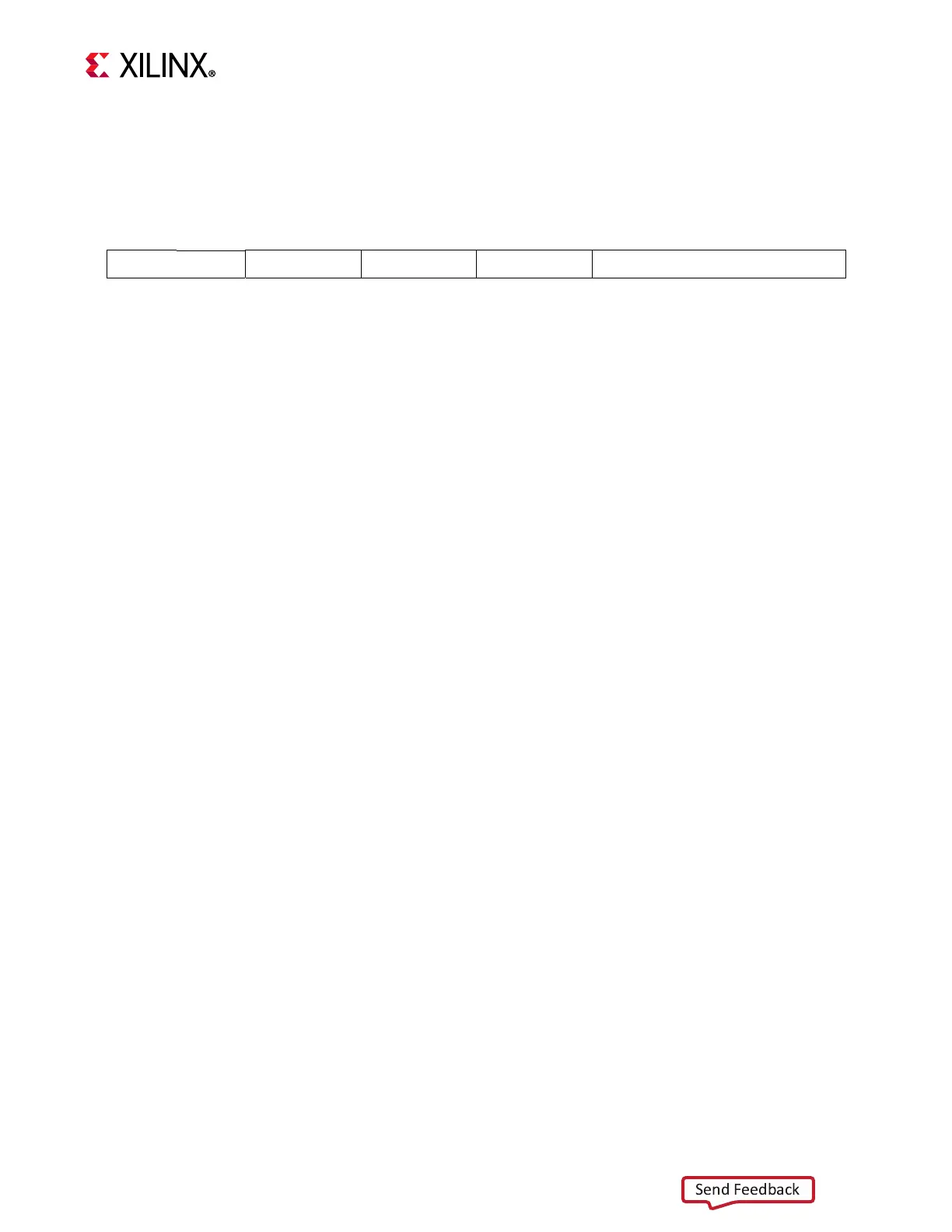

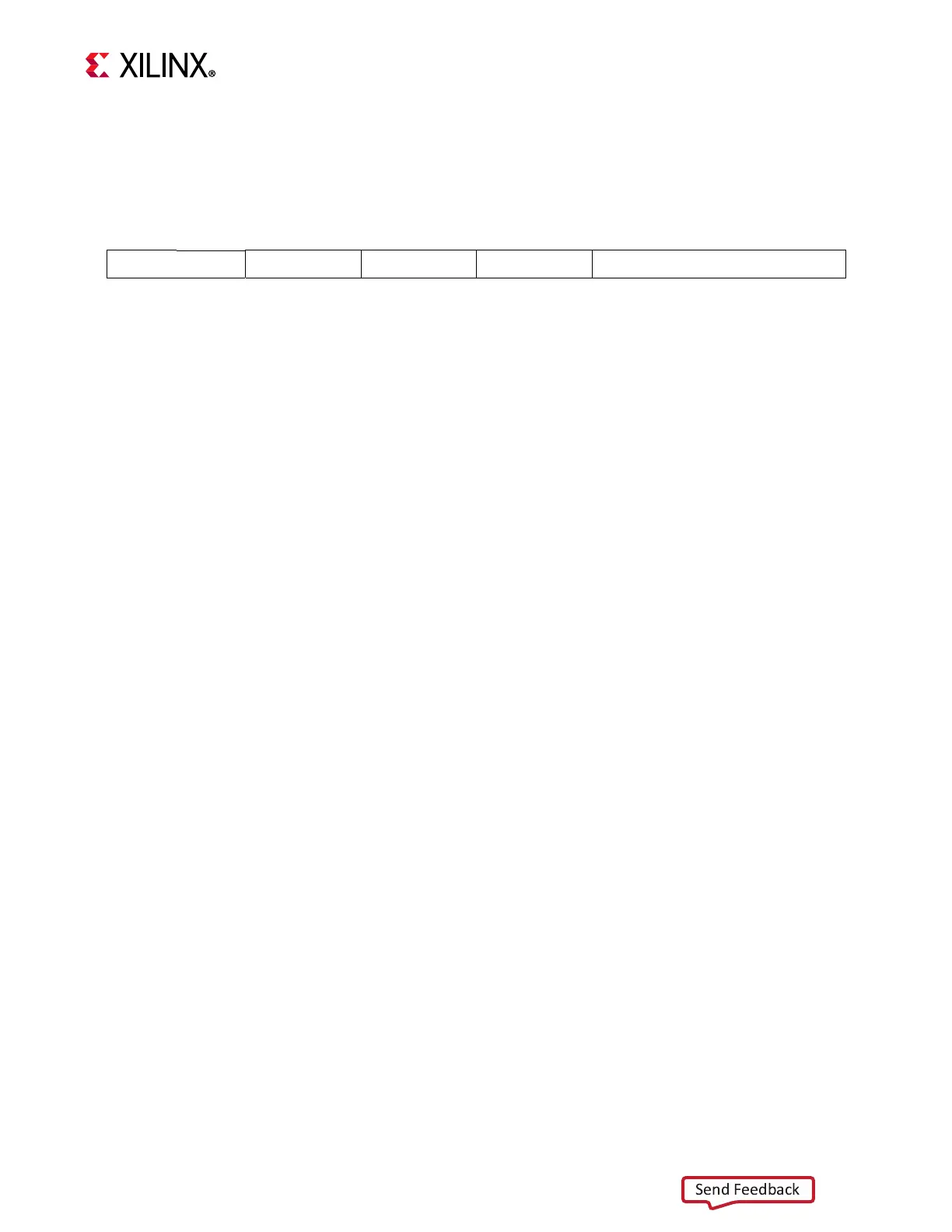

0 1 0 0 0 0 rD rA rB 0 0 0 0 0 0 0 0 0 0 0

0 6 11 16 21

31

Description

Multiplies the contents of registers rA and rB and puts the result in register rD. This is a 32-bit by 32-

bit multiplication that will produce a 64-bit result. The least significant word of this value is placed in

rD. The most significant word is discarded.

Pseudocode

(rD) ← LSW( (rA) × (rB) )

Registers Altered

•rD

Latency

• 1 cycle with C_AREA_OPTIMIZED=0 or 2

• 3 cycles with

C_AREA_OPTIMIZED=1

Note

This instruction is only valid if the target architecture has multiplier primitives, and if present, the

MicroBlaze parameter C_USE_HW_MUL is greater than 0.

Loading...

Loading...