MicroBlaze Processor Reference Guide 262

UG984 (v2018.2) June 21, 2018 www.xilinx.com

Chapter 5: MicroBlaze Instruction Set Architecture

mulhu

Multiply High Unsigned

mulhu

rD, rA, rB

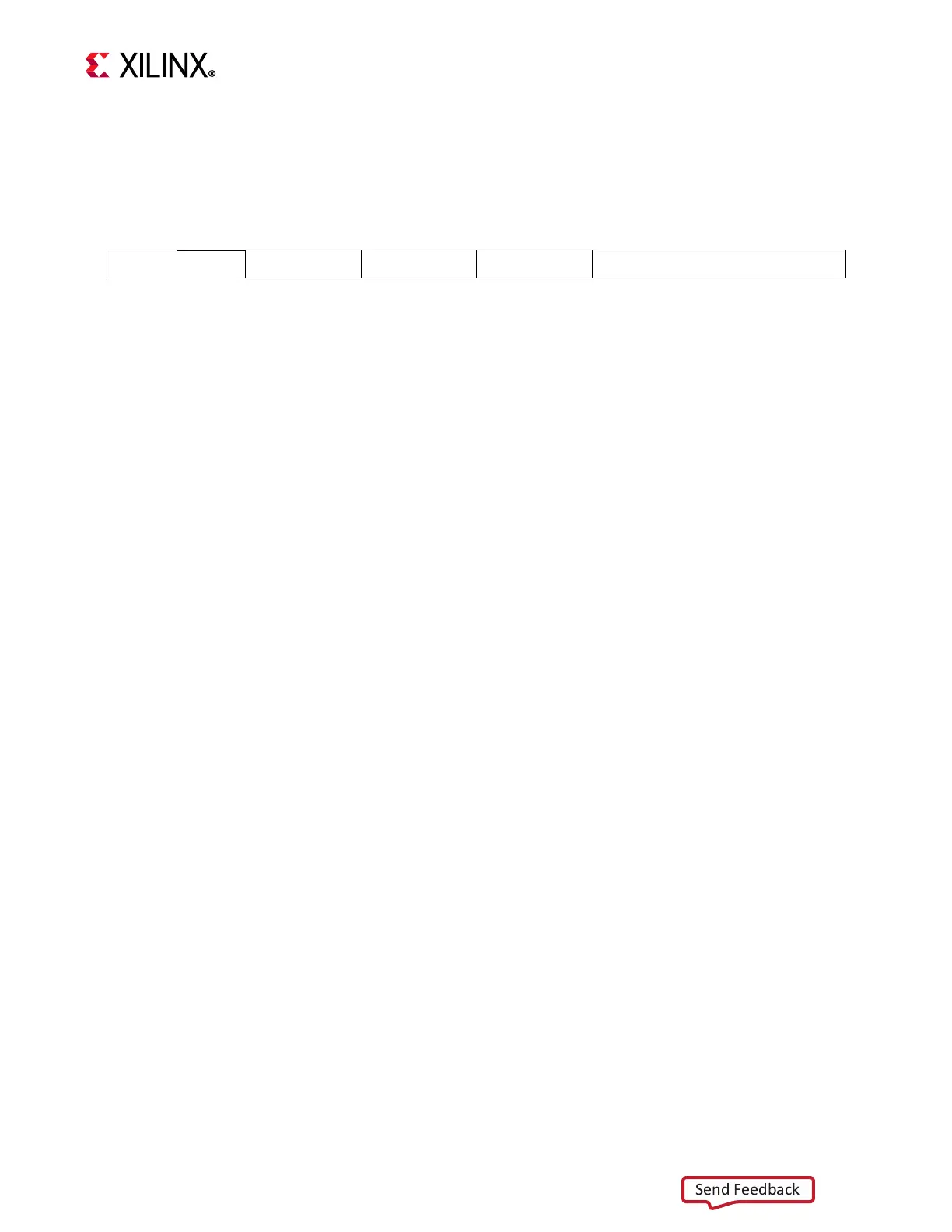

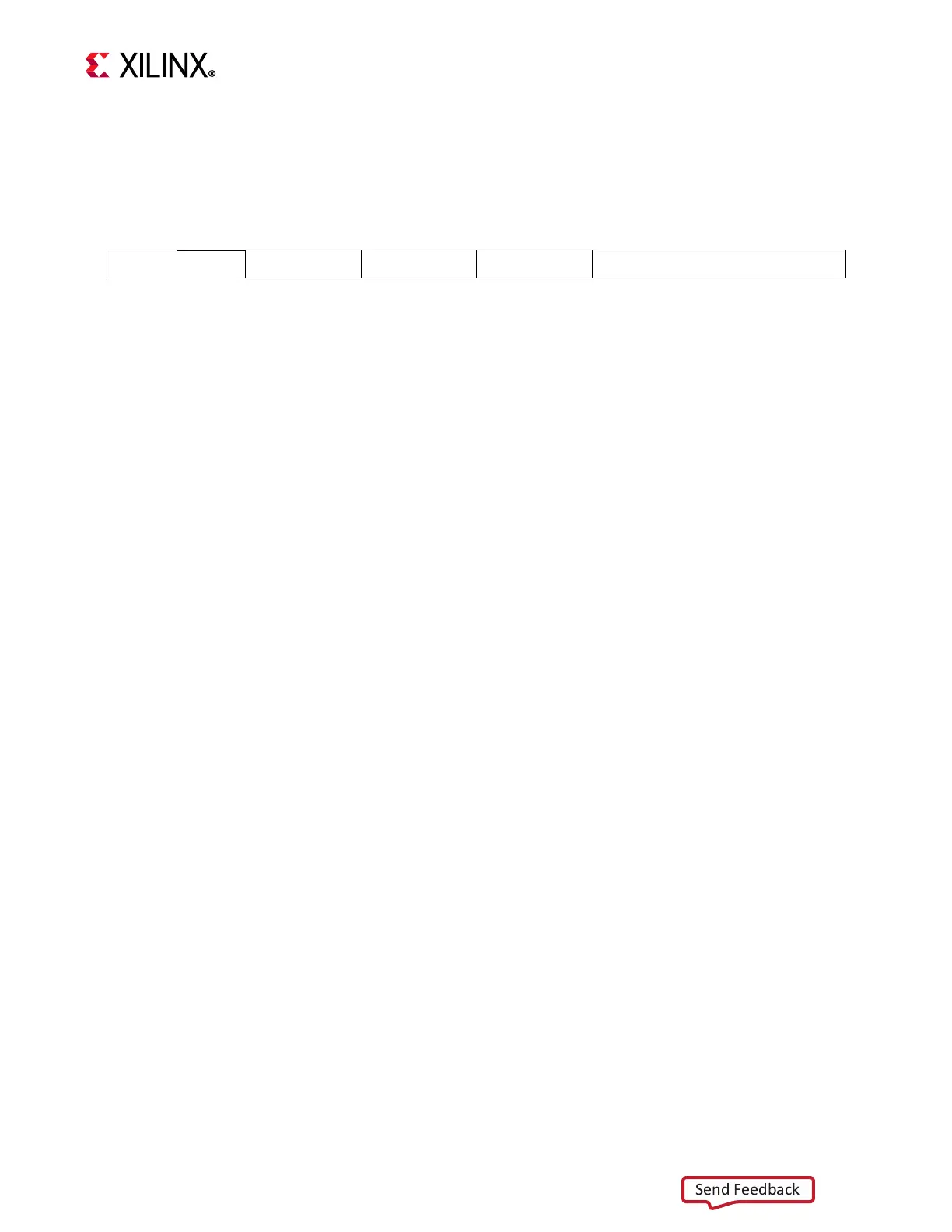

0 1 0 0 0 0 rD rA rB 0 0 0 0 0 0 0 0 0 1 1

0 6 11 16 21

31

Description

Multiplies the contents of registers rA and rB and puts the result in register rD. This is a 32-bit by 32-

bit unsigned multiplication that will produce a 64-bit unsigned result. The most significant word of

this value is placed in rD. The least significant word is discarded.

Pseudocode

(rD) ← MSW( (rA) × (rB) ), unsigned

Registers Altered

•rD

Latency

• 1 cycle with C_AREA_OPTIMIZED=0 or 2

• 3 cycles with

C_AREA_OPTIMIZED=1

Notes

This instruction is only valid if the target architecture has multiplier primitives, and if present, the

MicroBlaze parameter C_USE_HW_MUL is set to 2 (Mul64).

When MULHU is used, bit 30 and 31 in the MUL instruction must be zero to distinguish between the

two instructions. In previous versions of MicroBlaze, these bits were defined as zero, but the actual

values were not relevant.

Loading...

Loading...