MIPI CSI-2 RX Subsystem v4.0 40

PG232 July 02, 2019 www.xilinx.com

Chapter 3: Designing with the Subsystem

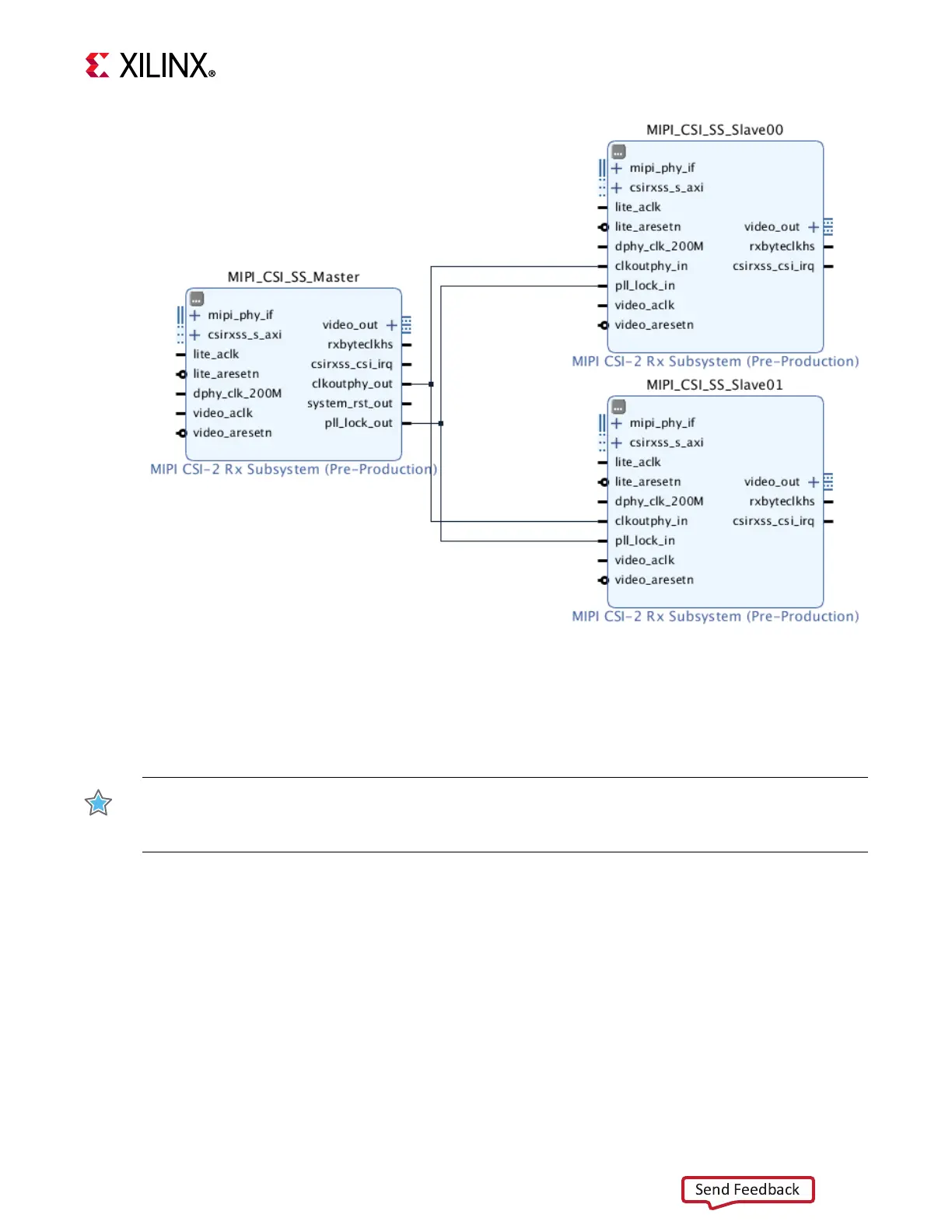

Note: The master and slave cores can be configured with the different line rates when operating

<1.5 Gb/s. However, when operating>1.5 Gb/s with Deskew detection feature enabled, the master

and slave cores should be configured with the same line rate when sharing clkoutphy within IO

bank. There must be at least one core with master mode in a system whose clocks can be shared with

slave mode cores.

IMPORTANT: Initialize all MIPI interfaces in the same HP IO Bank at the same time. For example,

multiple CSI-2 or D-PHY instances in a system. For more information on implementing multiple

interfaces in the same HP IO Bank, see UltraScale Architecture SelectIO Resources (UG571) [Ref 16].

X-Ref Target - Figure 3-3

Figure 3-3: Shared Logic in the Example Design

Loading...

Loading...