MIPI CSI-2 RX Subsystem v4.0 76

PG232 July 02, 2019 www.xilinx.com

Chapter 5: Application Example Design

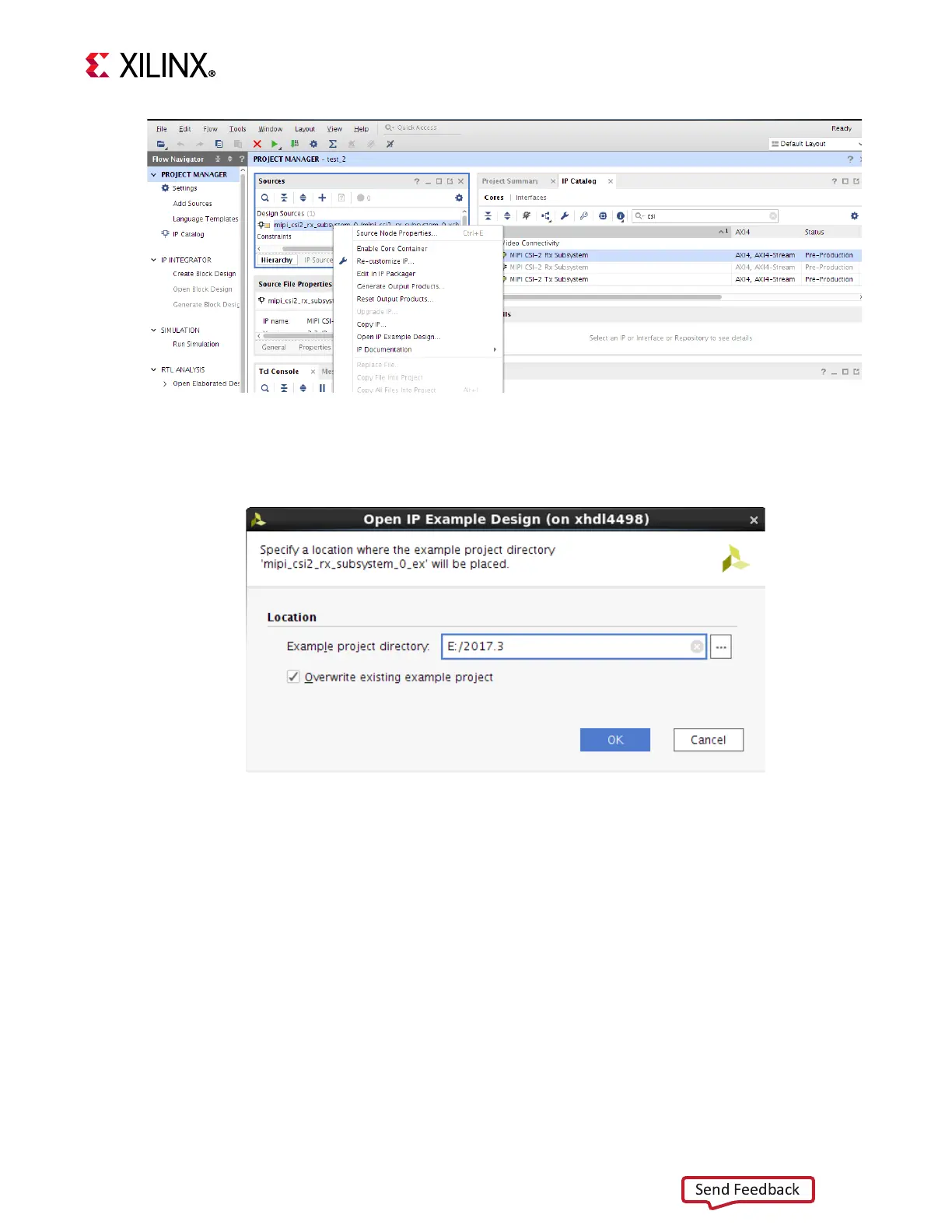

13. Choose the target project location, then click OK.

14. The overall system IPI block diagram of the ZCU102 based application example design

is generated. You may proceed to Run Synthesis, Implementation, and Generate

Bitstream to validate the design on board or use the IPI system as a reference for camera

capture to video display path. Click Generate Output Products option to see the

available synthesis options.

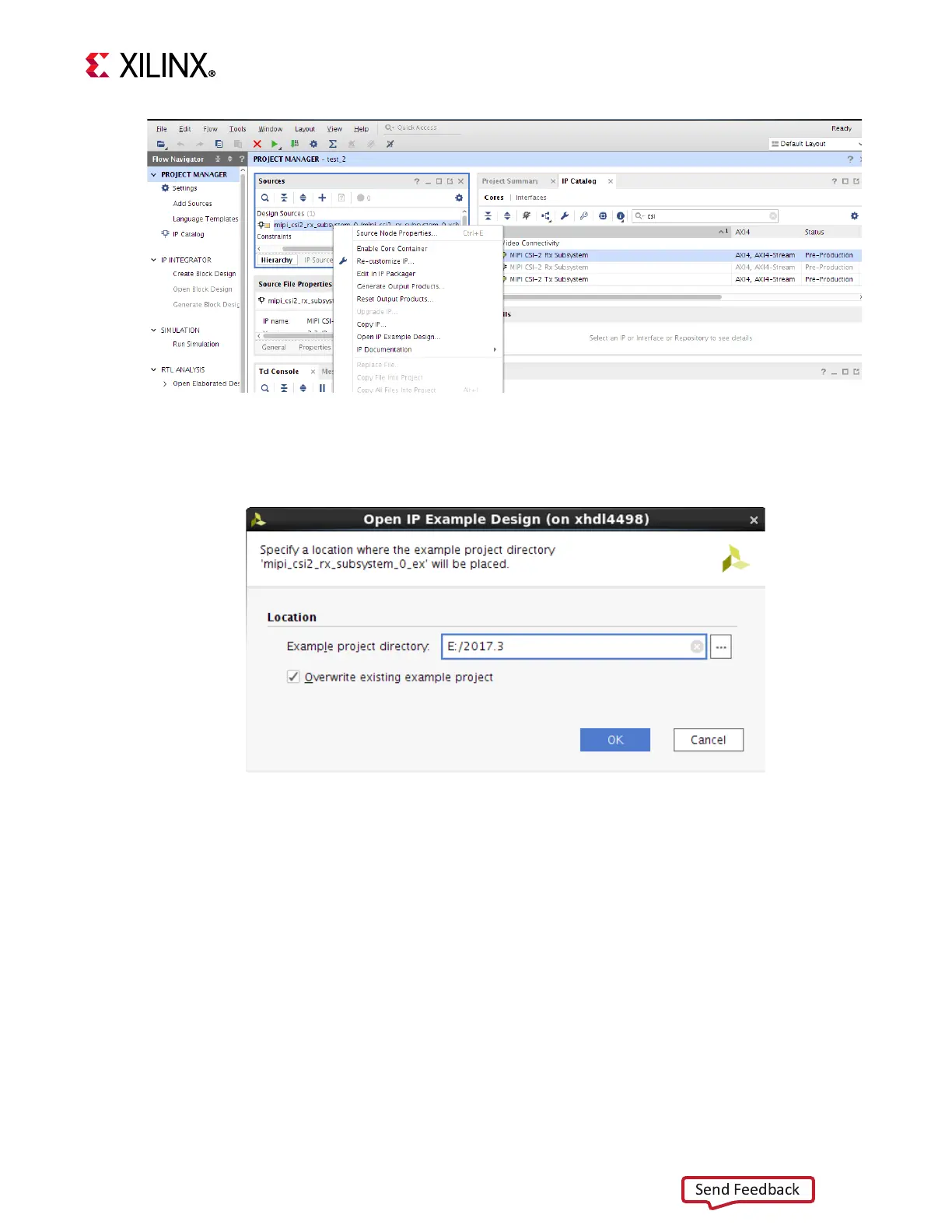

X-Ref Target - Figure 5-13

Figure 5-13: Vivado IDE - Open IP Example Design

X-Ref Target - Figure 5-14

Figure 5-14: Open IP Example Design - Select Example Project Directory

Loading...

Loading...