Zynq-7000 PCB Design Guide www.xilinx.com 64

UG933 (v1.8) November 7, 2014

Chapter 5: Processing System (PS) Power and Signaling

Note: For PS_DDR_DQxx, ensure that byte lines are kept together. PS_DDR_ADDR0 should always be

used. If bits must be omitted for chip select or other functionality, omit upper bit (PS_ADDR14)

instead.

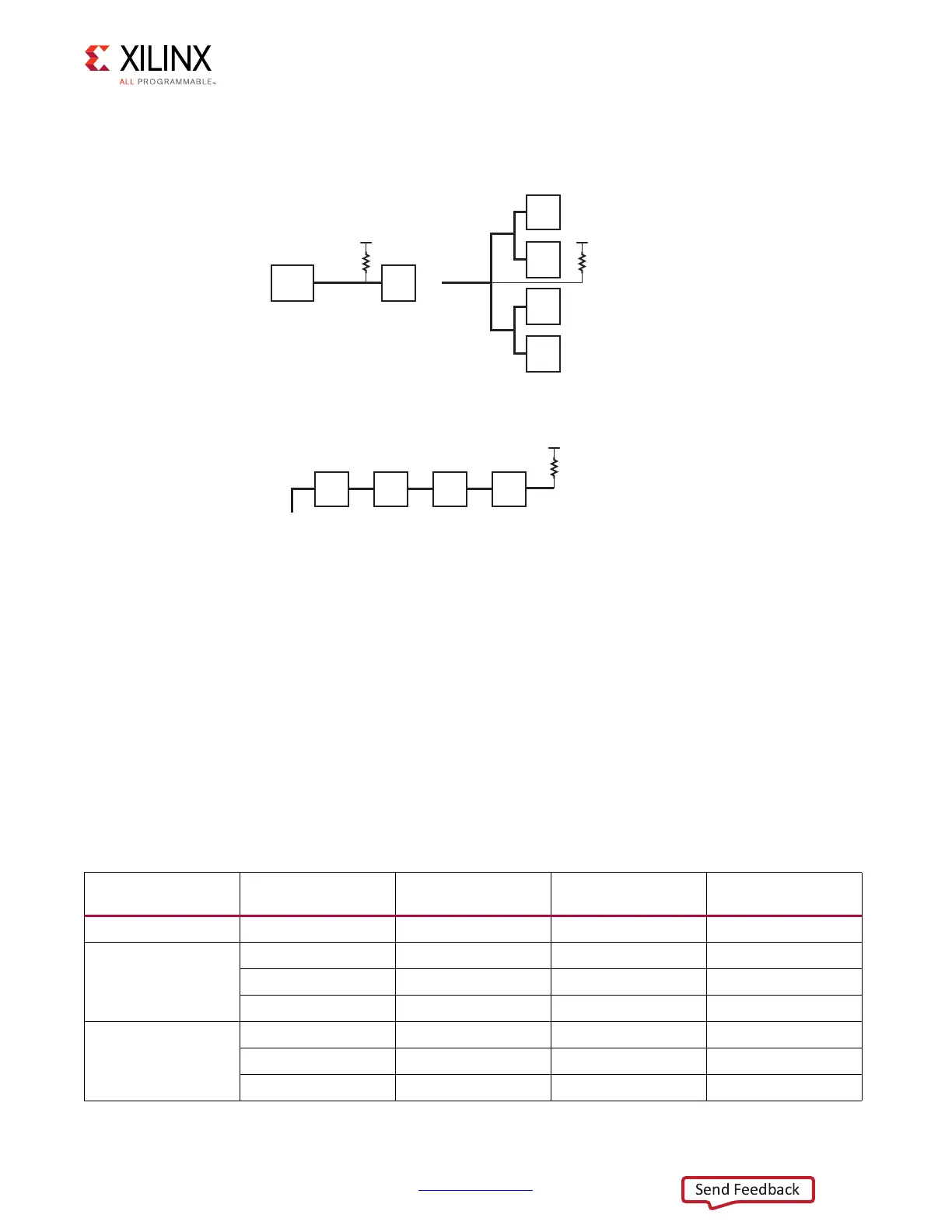

In a balanced T-branch configuration, trace lengths TL1, TL2 and Tsub shall be kept as short

as possible; Rterm shall be close to and balanced among the loads.

In a point-to-point configuration, Rterm shall be placed behind and close to the last load.

In the fly-by topology, TL0 should be kept from 0-64 mm, with TL1 14 mm ±0.1 mm, and

TL2 from 6-20 mm.

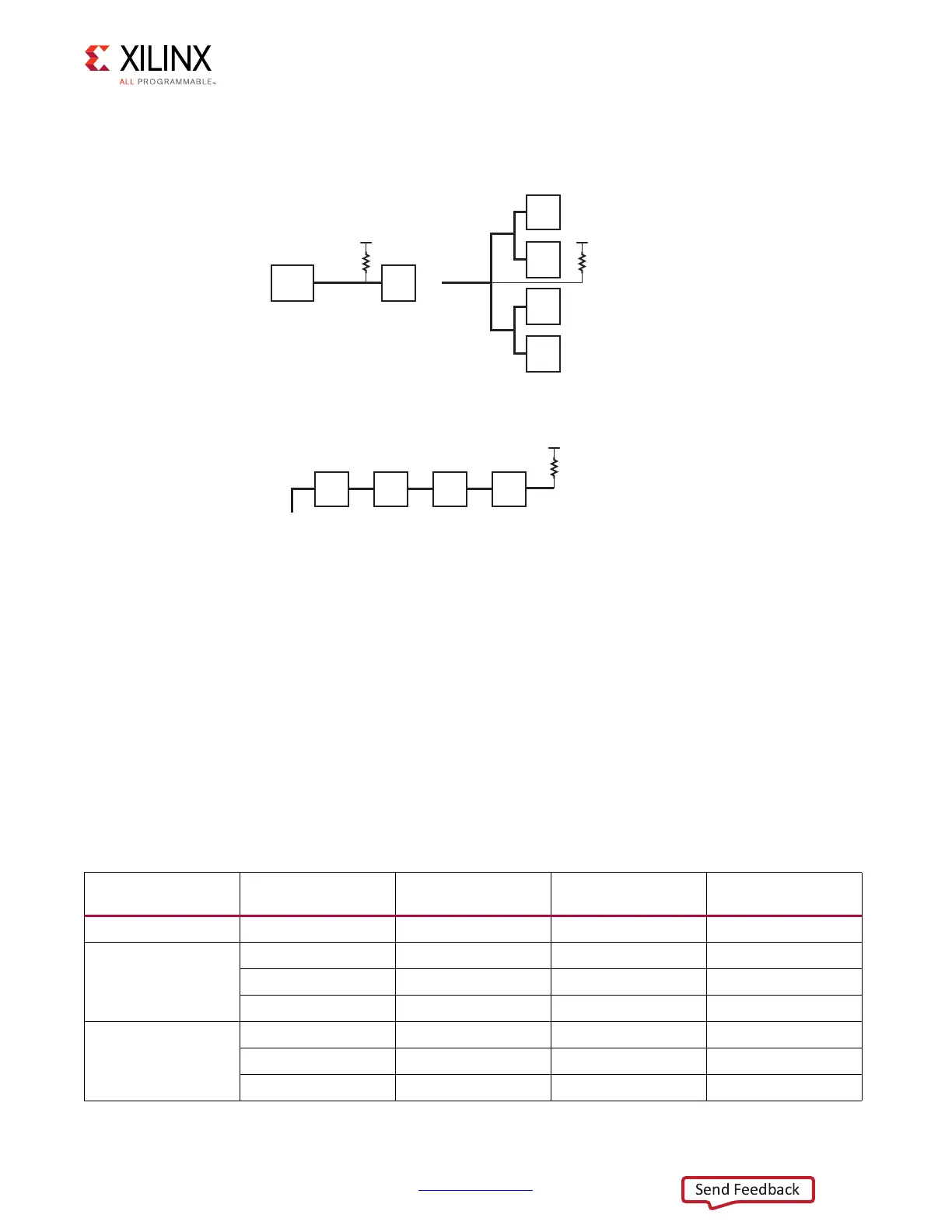

Table 5-12 shows the recommended routing topologies. Byte and bit swapping is allowed

to facilitate PCB routing, except for LPDDR2, which specifically forbids swapping. When

swapping bits, keep all bits within the same byte group.

X-Ref Target - Figure 5-8

Figure 5-8: DDR Routing Topologies

ZYNQ

DDR

VTT

VTT

Tsub

Tsub

TL2

TL0

TL1

Rterm Rterm

Balanced T-branchPoint-to-point

UG585_c30_07_091913

DDR

DDR

DDR

DDR

DDR DDR DDR DDR

VTT

Rterm

TL0

TL1 TL1 TL1

TL2

Fly-by

Table 5-12: DDR Routing Topology

Signal Group LPDDR2 DDR2 DDR3/3L

Number of DDR

Devices

Data Point-to-point Point-to-point Point-to-point

Clock

Point-to-point Point-to-point Point-to-point 1

T-branch T-branch Fly-by 2

N/A T-branch Fly-by 4

Address,

Command,

Control

Point-to-point Point-to-point Point-to-point 1

T-branch T-branch Fly-by/T-branch 2

N/A T-branch Fly-by/T-branch 4

Loading...

Loading...