UG-570 AD9361 Reference Manual

| Page 110 of 128

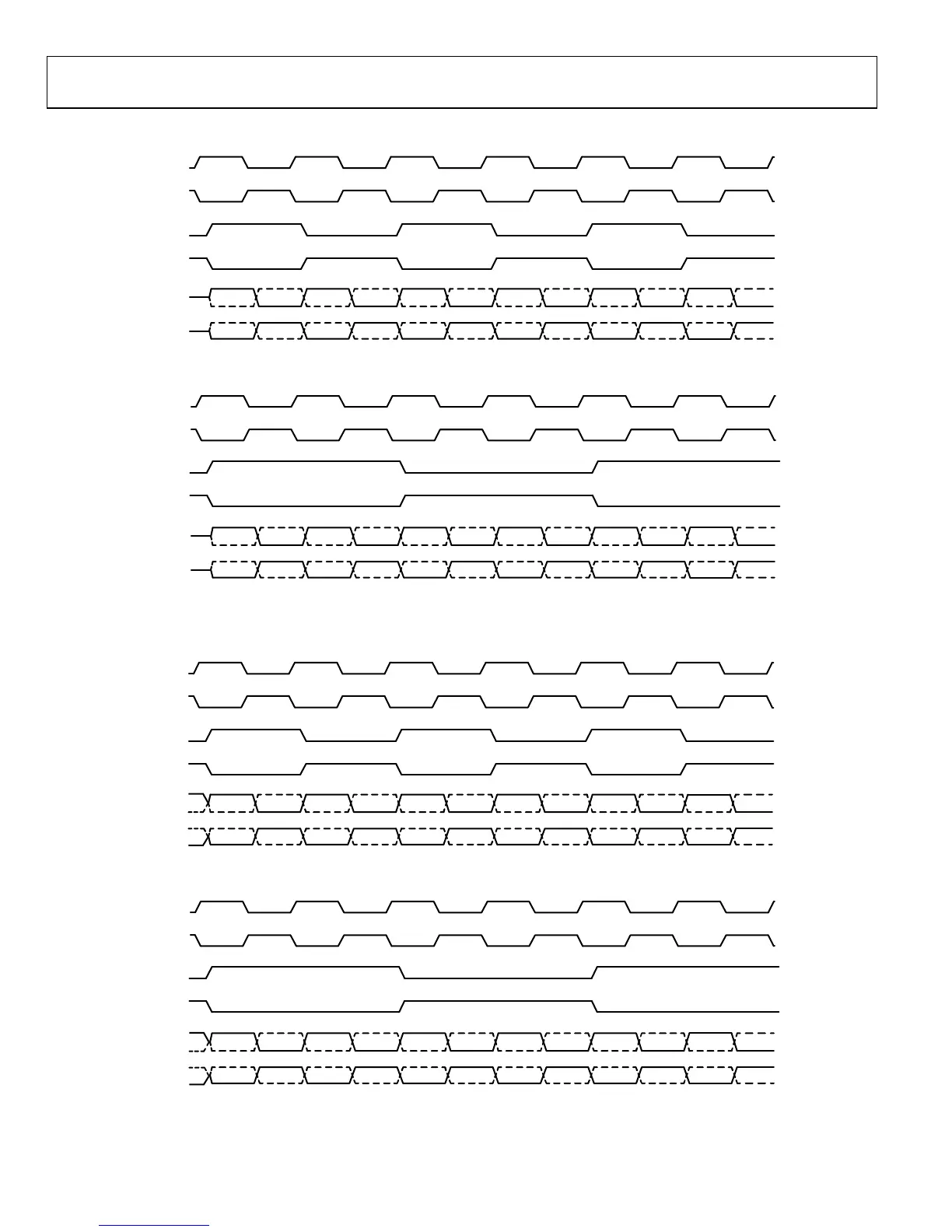

Fig

ure 79. Receive Data Path, LVDS

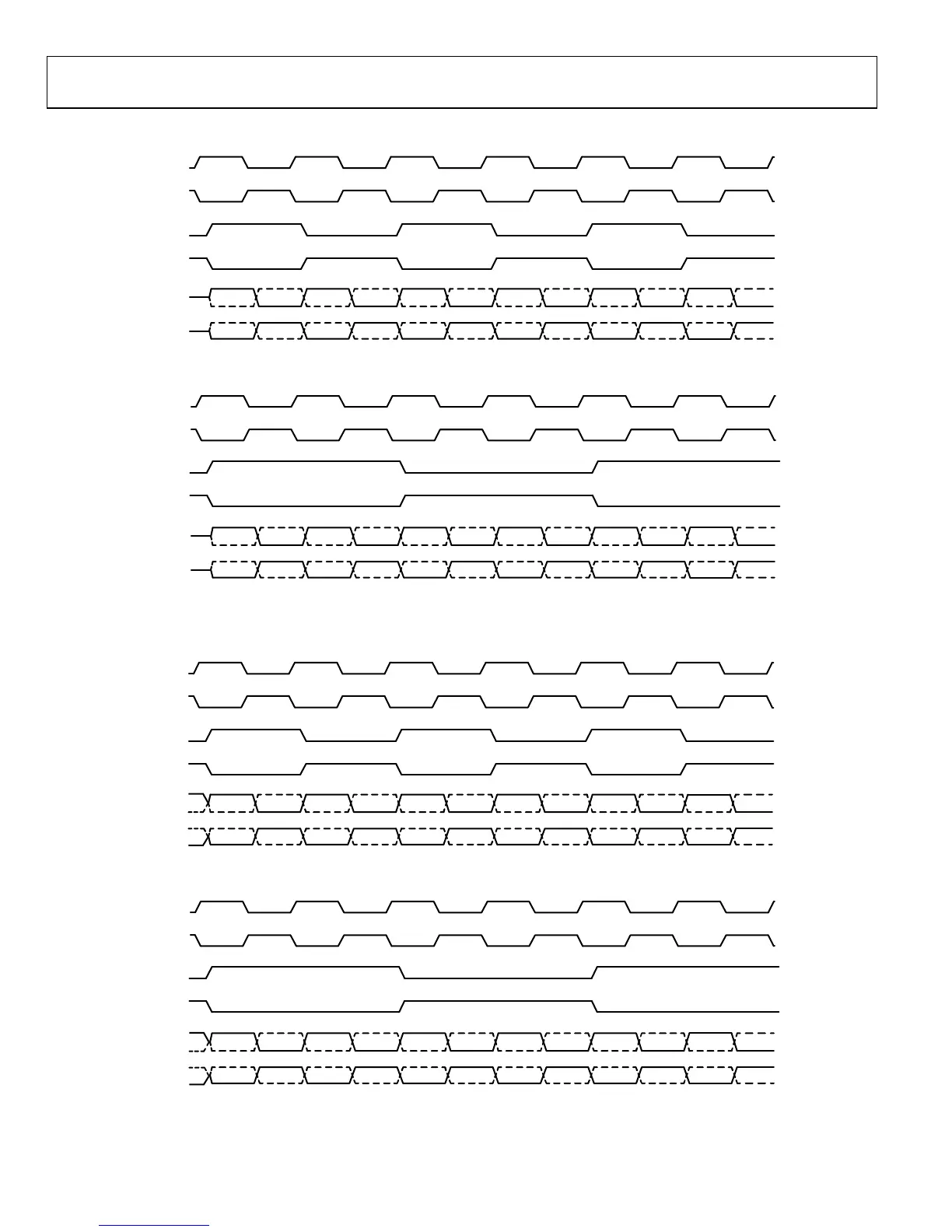

Fig

ure 80. Transmit Data Path, LVDS

DATA_CLK_P

RX_FRAME_P

RX_D[5:0]_P

RX_D[5:0]_N

DATA_CLK_N

RX_FRAME_N

1R1T, DDR, FDD, LVDS, 0x010 = 0xC8, 0x011 = 0x00, 0x012 = 0x10

R_I[11:6]

R_Q[11:6] R_I[5:0] R_Q[5:0]

R_I[11:6]

R_Q[11:6] R_I[5:0] R_Q[5:0]

R_I[11:6]

R_Q[11:6] R_I[5:0] R_Q[5:0]

R_I[11:6]

R_Q[11:6] R_I[5:0] R_Q[5:0]

R_I[11:6]

R_Q[11:6] R_I[5:0] R_Q[5:0]

R_I[11:6]

R_Q[11:6] R_I[5:0] R_Q[5:0]

11668-080

DATA_CLK_P

RX_FRAME_P

RX_D[5:0]_P

RX_D[5:0]_N

DATA_CLK_N

RX_FRAME_N

2R2T, DDR, FDD, LVDS, 0x010 = 0xC8, 0x011 = 0x00, 0x012 = 0x10

R1_I[11:6]

R1_Q[11:6] R1_I[5:0] R1_Q[5:0]

R1_I[11:6]

R1_Q[11:6]

R1_I[5:0] R1_Q[5:0]

R2_I[11:6]

R2_Q[11:6] R2_I[5:0] R2_Q[5:0]

R2_I[11:6]

R2_Q[11:6] R2_I[5:0] R2_Q[5:0]

R1_I[11:6]

R1_Q[11:6] R1_I[5:0] R1_Q[5:0]

R1_I[11:6]

R1_Q[11:6] R1_I[5:0] R1_Q[5:0]

FB_CLK_P

TX_FRAME_P

TX_D[5:0]_P

TX_D[5:0]_N

FB_CLK_N

TX_FRAME_N

1R1T, DDR, FDD, LVDS, 0x010 = 0xC8, 0x011 = 0x00, 0x012 = 0x10

T_I[11:6]

T_Q[11:6] T_I[5:0] T_Q[5:0]

T_I[11:6]

T_Q[11:6] T_I[5:0] T_Q[5:0]

T_I[11:6]

T_Q[11:6] T_I[5:0] T_Q[5:0]

T_I[11:6]

T_Q[11:6] T_I[5:0] T_Q[5:0]

T_I[11:6]

T_Q[11:6] T_I[5:0] T_Q[5:0]

T_I[11:6]

T_Q[11:6] T_I[5:0] T_Q[5:0]

11668-081

FB_CLK_P

TX_FRAME_P

TX_D[5:0]_P

TX_D[5:0]_N

FB_CLK_N

TX_FRAME_N

2R2T, DDR, FDD, LVDS, 0x010 = 0xC8, 0x011 = 0x00, 0x012 = 0x10

T1_I[11:6]

T1_Q[11:6] T1_I[5:0] T1_Q[5:0]

T1_I[11:6]

T1_Q[11:6]

T1_I[5:0] T1_Q[5:0]

T2_I[11:6]

T2_Q[11:6] T2_I[5:0] T2_Q[5:0]

T2_I[11:6]

T2_Q[11:6] T2_I[5:0] T2_Q[5:0]

T1_I[11:6]

T1_Q[11:6] T1_I[5:0] T1_Q[5:0]

T1_I[11:6]

T1_Q[11:6] T1_I[5:0] T1_Q[5:0]

0

0

0

0

Loading...

Loading...