132

2467S–AVR–07/09

ATmega128

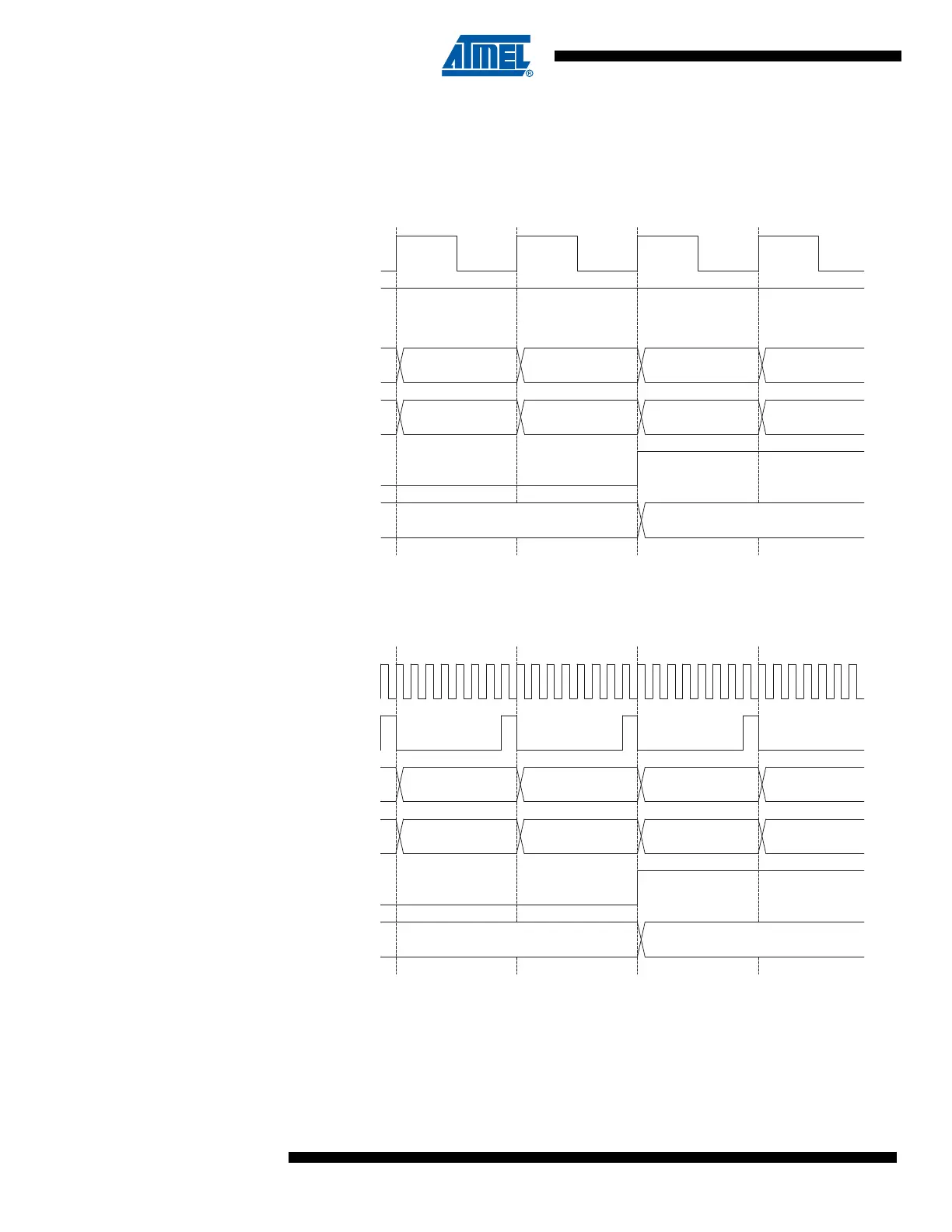

Figure 57 shows the count sequence close to TOP in various modes. When using phase and

frequency correct PWM mode the OCRnx Register is updated at BOTTOM. The timing diagrams

will be the same, but TOP should be replaced by BOTTOM, TOP-1 by BOTTOM+1 and so on.

The same renaming applies for modes that set the TOVn flag at BOTTOM.

Figure 57. Timer/Counter Timing Diagram, no Prescaling

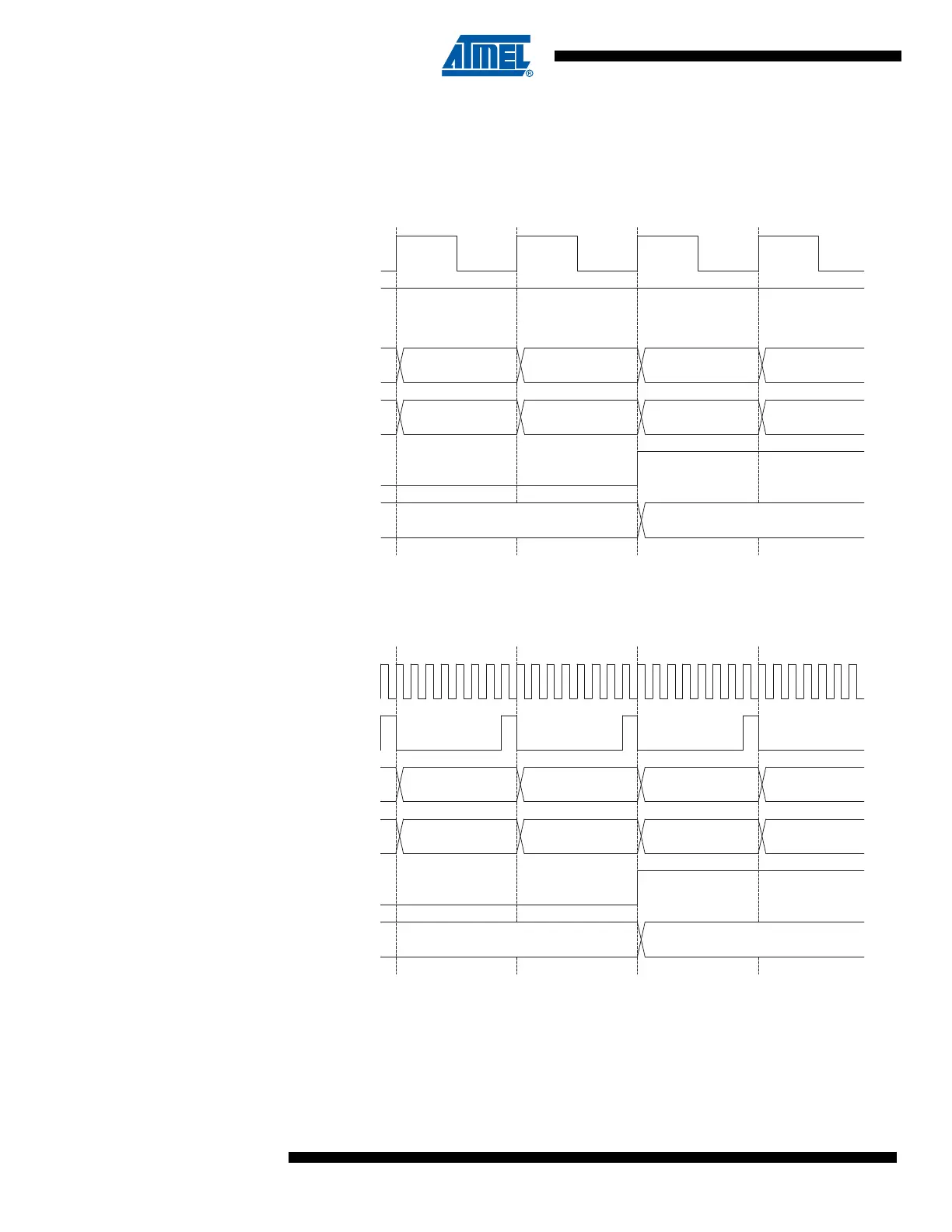

Figure 58 shows the same timing data, but with the prescaler enabled.

Figure 58. Timer/Counter Timing Diagram, with Prescaler (f

clk_I/O

/8)

TOVn (FPWM)

and ICFn (if used

as TOP)

OCRnx

(Update at TOP)

TCNTn

(CTC and FPWM)

TCNTn

(PC and PFC PWM)

TOP - 1 TOP TOP - 1 TOP - 2

Old OCRnx Value New OCRnx Value

TOP - 1 TOP BOTTOM BOTTOM + 1

clk

Tn

(clk

I/O

/1)

clk

I/O

TOVn

(FPWM)

and ICFn

(if used

as TOP)

OCRnx

(Update at TOP)

TCNTn

(CTC and FPWM)

TCNTn

(PC and PFC PWM)

TOP - 1 TOP TOP - 1 TOP - 2

Old OCRnx Value New OCRnx Value

TOP - 1 TOP BOTTOM BOTTOM + 1

clk

I/O

clk

Tn

(clk

I/O

/8)

Loading...

Loading...