60

_____________________________________________________________________________________________

7.2 Communication

______________________________________________________________________________________________

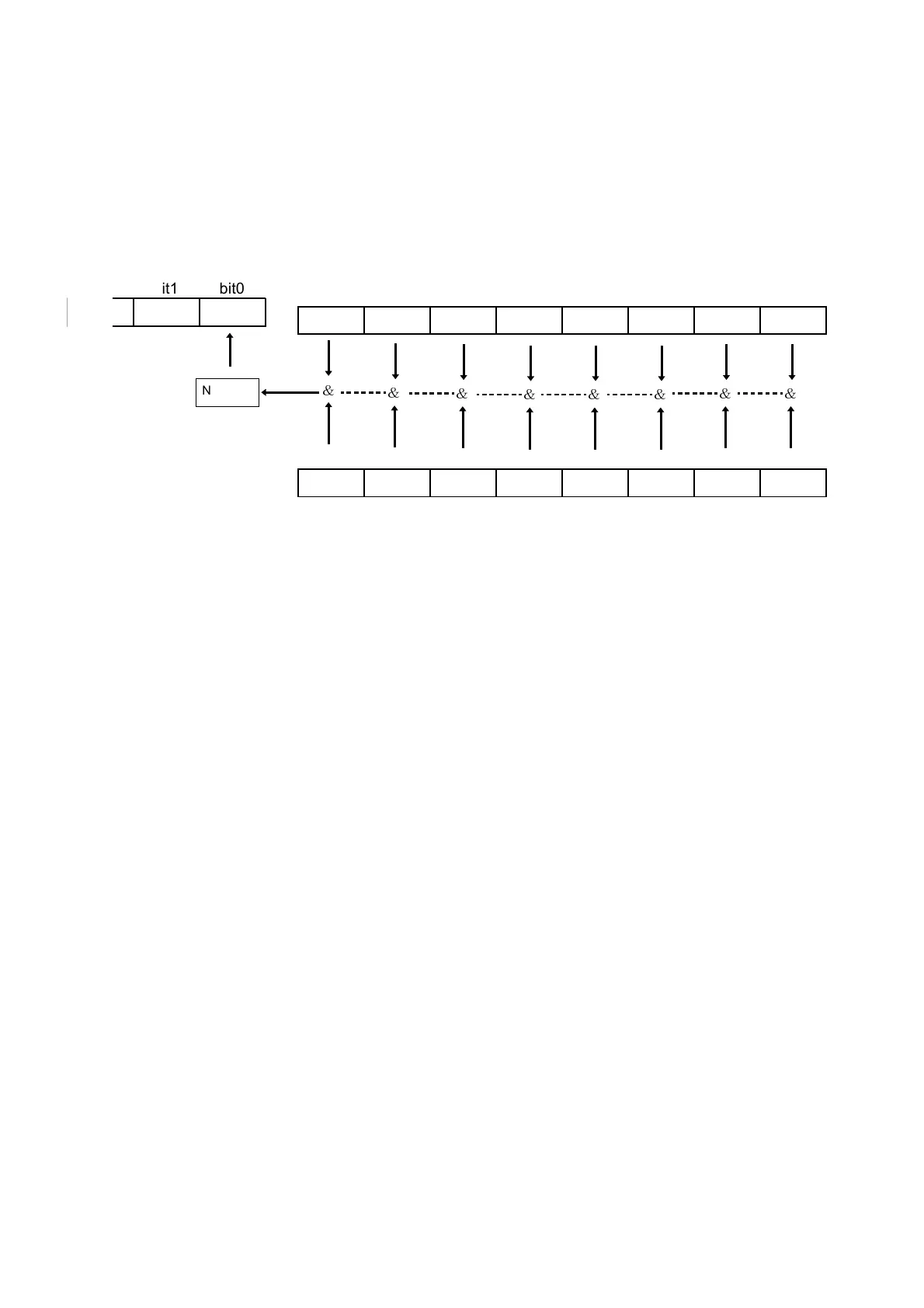

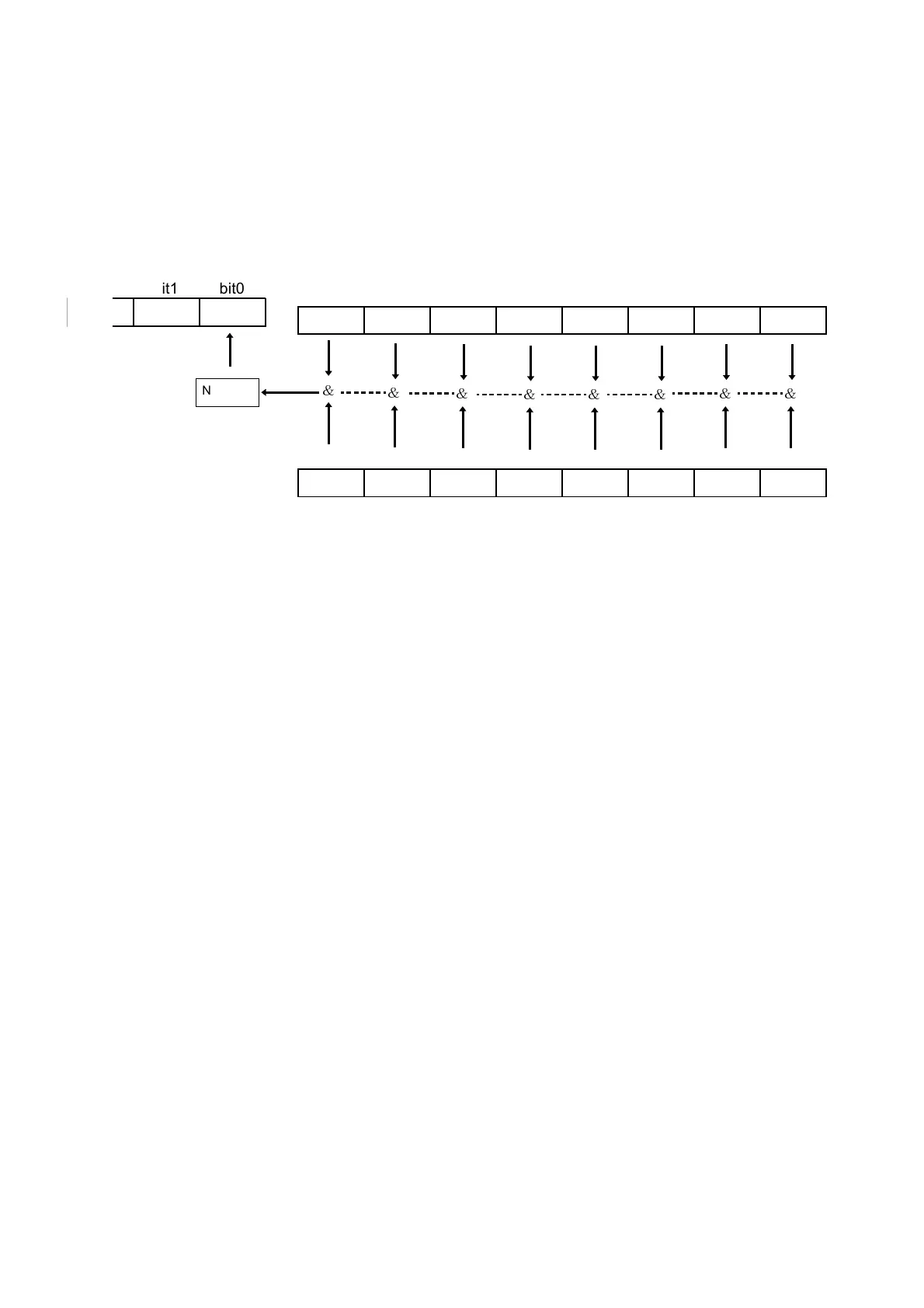

bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0

Not used Not used

-OF +OF HI IN LO EOC

Event status re

isters 0

SESR0

bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0

Not used Not used

-OF +OF HI IN LO EOC

Event status enable re

isters 0

ESER0

&

Not used

&

& &

&&&

&

bit1 bit0

Not used

ESB0

Specific Event Registers

(1) Event status register 0

8-bit event status registers are provided for managing events on the

3237/38/39. If any bit in one of these event status registers is set to 1 (after

masking by the corresponding event status enable register), bit 0 of the status

byte register (ESB0) is set to 1.

The event status register 0 is cleared in the following four situations:

① When a ∗CLS command is received.

② When an ∗ESR? query is received.

③ When the unit is powered on.

④ When the I/F is Switched.

Loading...

Loading...