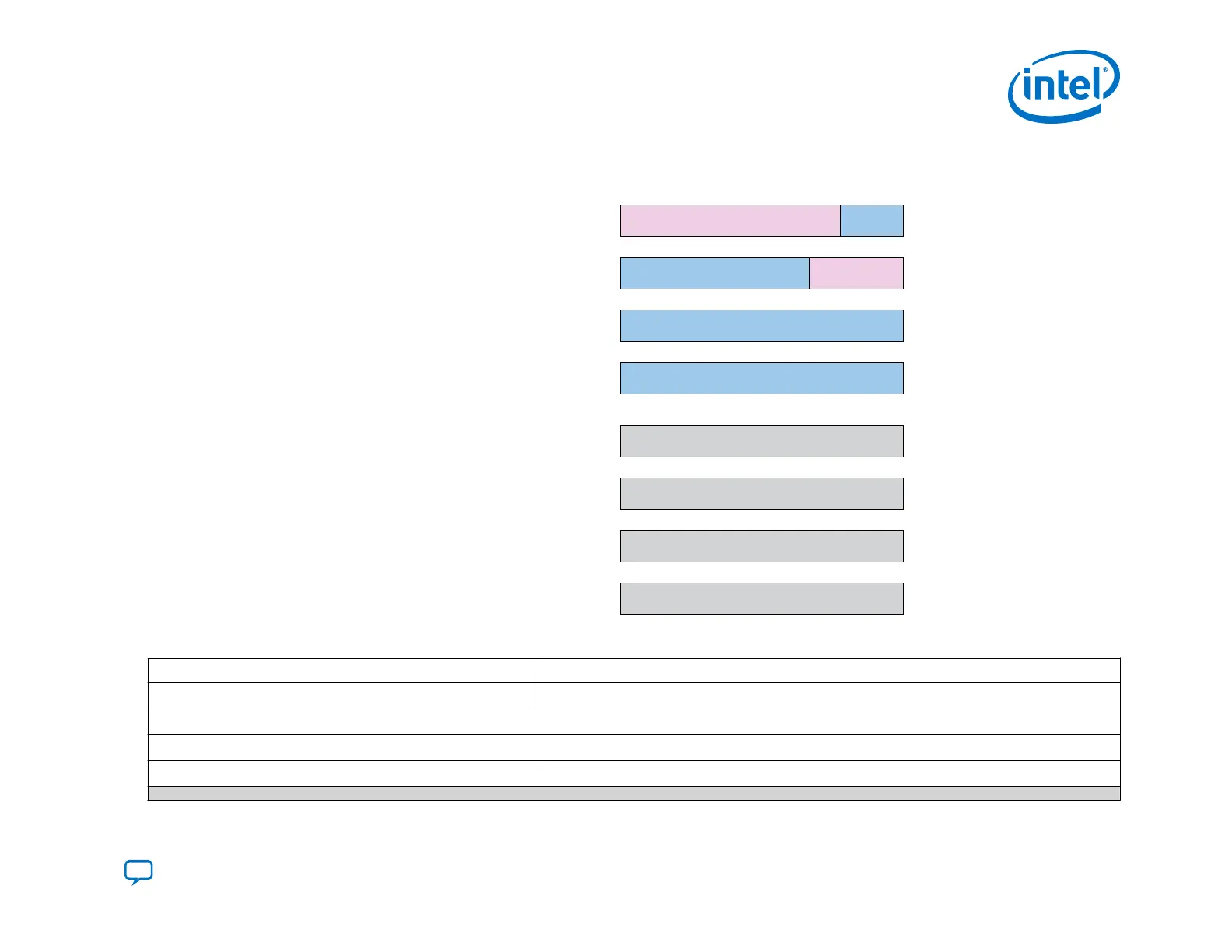

Figure 29. Page Start Address, End Address, and Page-Valid Bit Stored as Option Bits

The Page-Valid bits indicate whether each page is successfully programmed. The PFL II IP core sets the Page-Valid bits after successfully programming the pages.

Bit 2...Bit 0Bit 7...Bit 3

Bit 7...Bit 0

Bit 7...Bit 0

Bit 7...Bit 0

Bit 7...Bit 0

Bit 7...Bit 0

Bit 7...Bit 0

Bit 7...Bit 1 Bit 0

0x002002

0x002003

0x002000

0x002001 Page Start Address [17:13]

Page Start Address [25:18]

Page Start Address [33:26]

Page End Address [9:2]

Page End Address [17:10]

Page End Address [25:18]

0x002004

0x002005

0x002006

Page End Address [33:26]

Page ValidReserved

Reserved

0x002007

(For flash byte addressing mode)

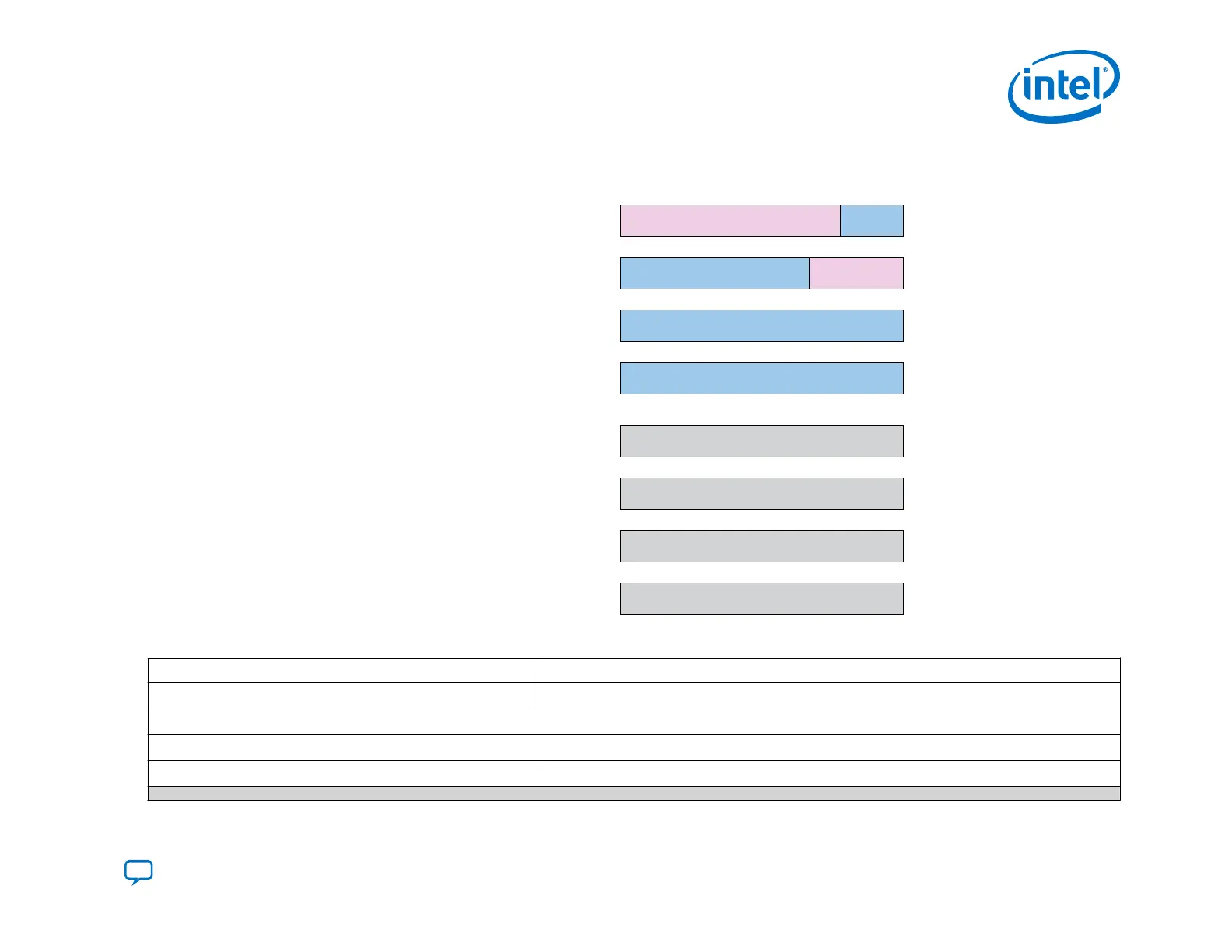

Table 15. Byte Address Range for CFI Flash Memory Devices with Different Densities

CFI Device (Megabit) Address Range

8

0x0000000–0x00FFFFF

16

0x0000000–0x01FFFFF

32

0x0000000–0x03FFFFF

64

0x0000000–0x07FFFFF

continued...

3. Intel Agilex Configuration Schemes

UG-20205 | 2019.10.09

Send Feedback

Intel

®

Agilex

™

Configuration User Guide

71

Loading...

Loading...