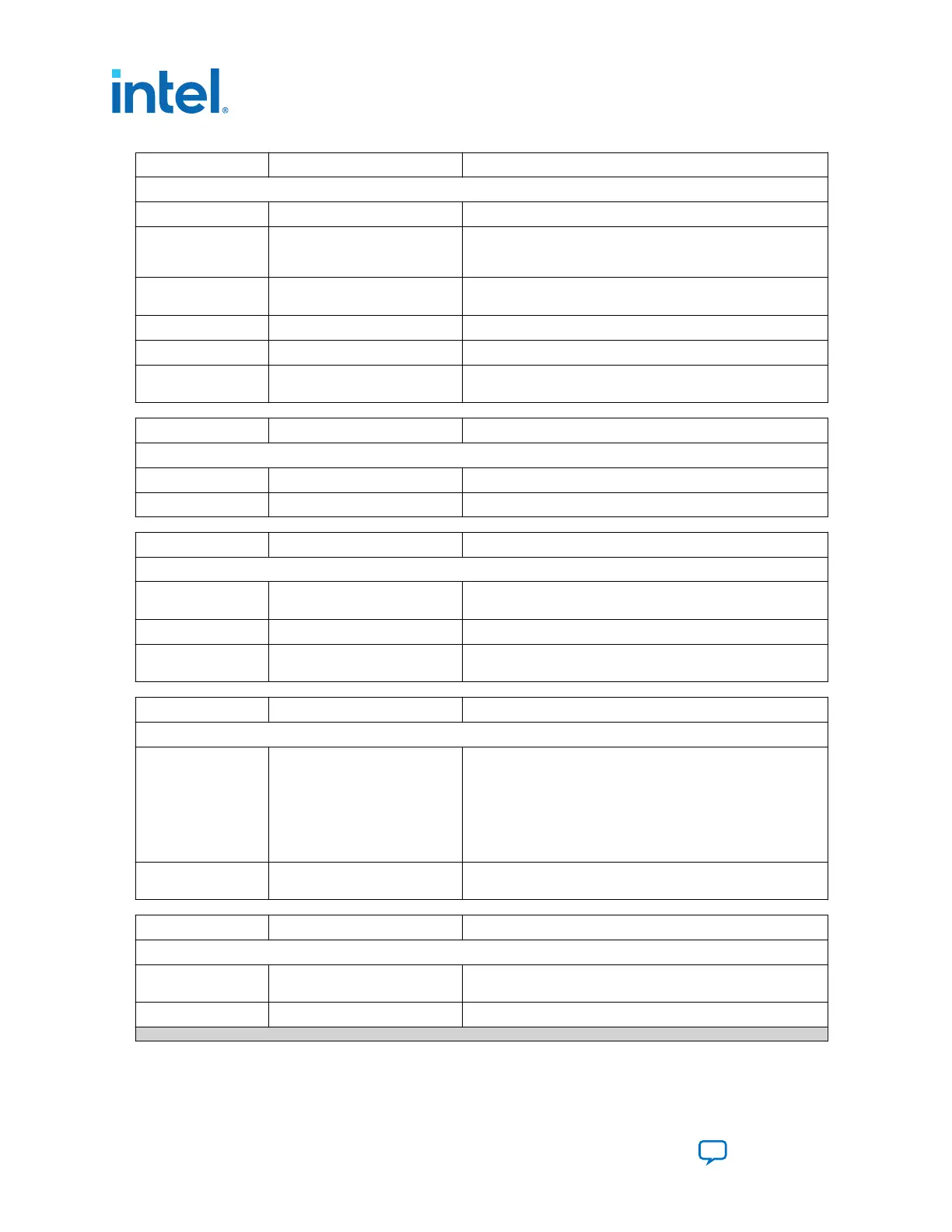

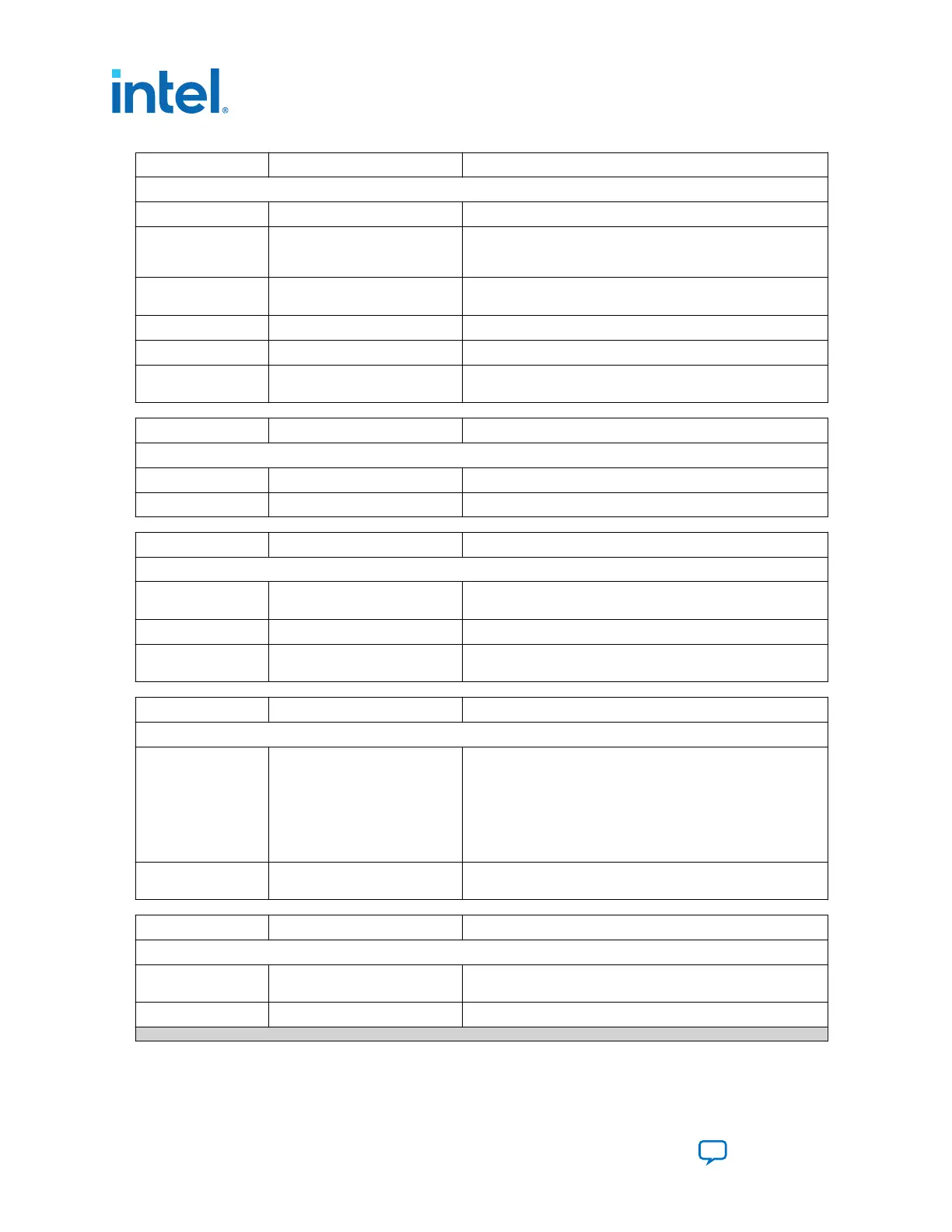

Board Reference Type Description

Clock Circuitry

X4 50-MHz oscillator 50.000-MHz crystal oscillator for general purpose logic.

U26 Quad-output oscillator Si5338 programmable oscillator for clock control GUI. (Defaults

CLK[0:3] = 270MHz, 644.53125MHz, 644.53125MHz,

133.33MHz)

U14 Quad-output oscillator Si5338 programmable oscillator for clock control GUI. (Defaults

CLK[0:3] = 100MHz, 625MHz, 625MHz, 302.083333MHz)

J6 Clock input SMA connector Signal: CLKIN_SMA

J7 Clock output SMA connector Signal: SMA_CLK_OUT

J20, J21 SDI (Serial Digital Interface)

transceiver connectors

Two sub-miniature version B (SMB) connectors. Drives serial

data input/output to or from SDI video port.

Board Reference Type Description

Transceiver Interfaces

J15 SMA connector SMA_TX_N from the left transceiver bank - 1H

J16 SMA connector SMA_TX_P from the left transceiver bank - 1H

Board Reference Type Description

General User Input/Output

SW2 FPGA user DIP switch Octal user DIP switches. When the switch is ON, a logic 0 is

selected.

S1, S2, S3 General user push buttons Three user push buttons. Driven low when pressed.

D3, D4, D5, D6, D7,

D8, D9, D10

User defined LEDs Eight bi-color user LEDs. Illuminates when driven low.

Board Reference Type Description

Memory Devices

J14 HiLo Connector One x72 memory interface supporting DDR3 (x72), DDR4

(x72), QDR4 (x36), and RLDRAM 3 (x36).

This development kit includes three plugin modules

(daughtercards) that use the HiLo connector:

• DDR4 memory (x72) 1200 MHz

• DDR3 memory (x72) 1066 MHz, Ping Pong PHY.

• RLDRAM3 memory (x36) 1,200 MHz

U4, U5 Flash memory ICS - 1GBIT STRATA FLASH, 16-BIT DATA,

VCC=VCCQ=1.7V-2.0V, 64-BALL EASY BGA (10MM X 8MM)

Board Reference Type Description

Communication Ports

J22 PCI Express x8 edge connector Made of gold-plated edge fingers for up to ×8 signaling in

either Gen1, Gen2, or Gen3 mode.

J1, J2 FMC Port FPGA mezzanine card ports A and B.

continued...

6. Board Components

683526 | 2023.07.12

Intel

®

Arria

®

10 FPGA Development Kit User Guide

Send Feedback

58

Loading...

Loading...