Basic System Configuration Guide System Management

Edition: 01 3HE 11010 AAAC TQZZA 243

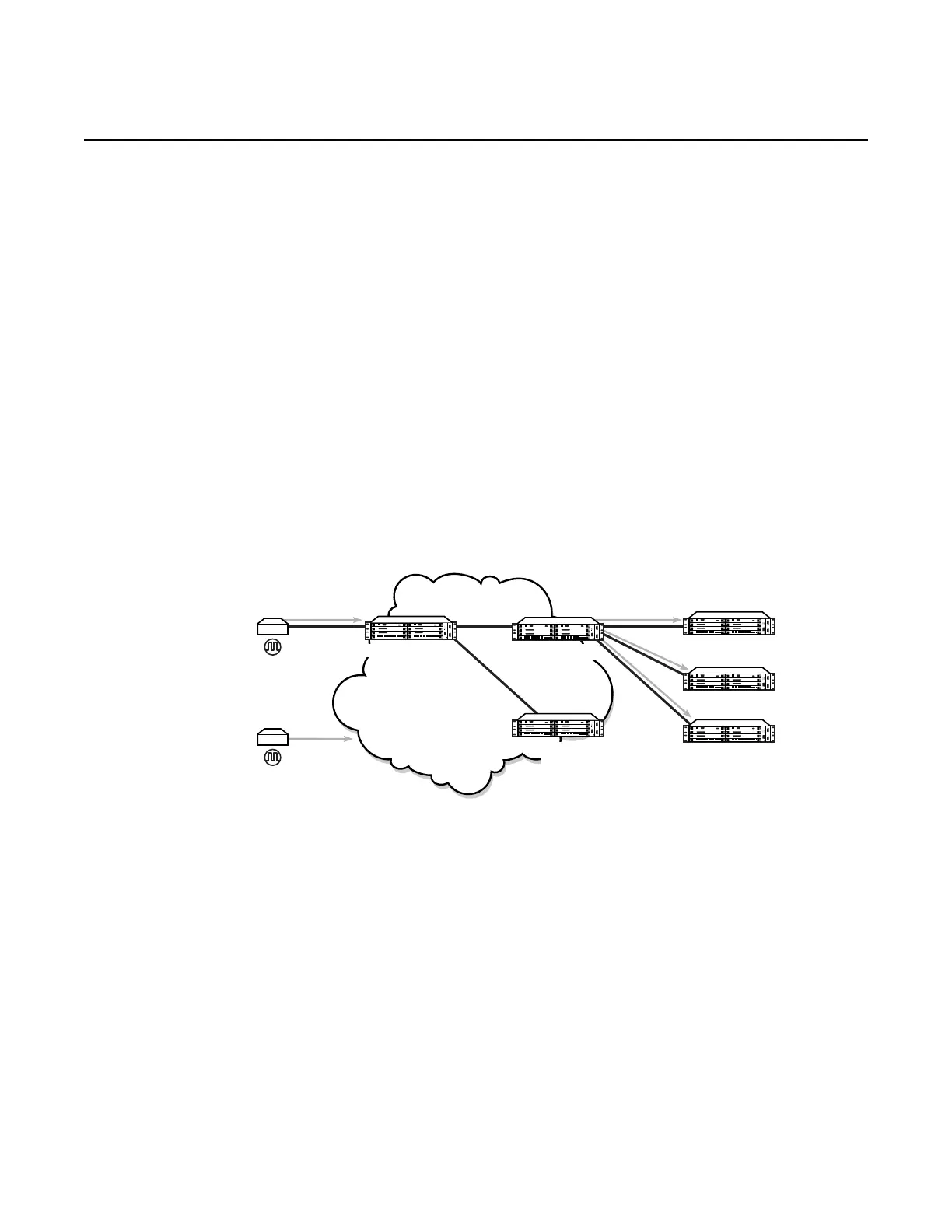

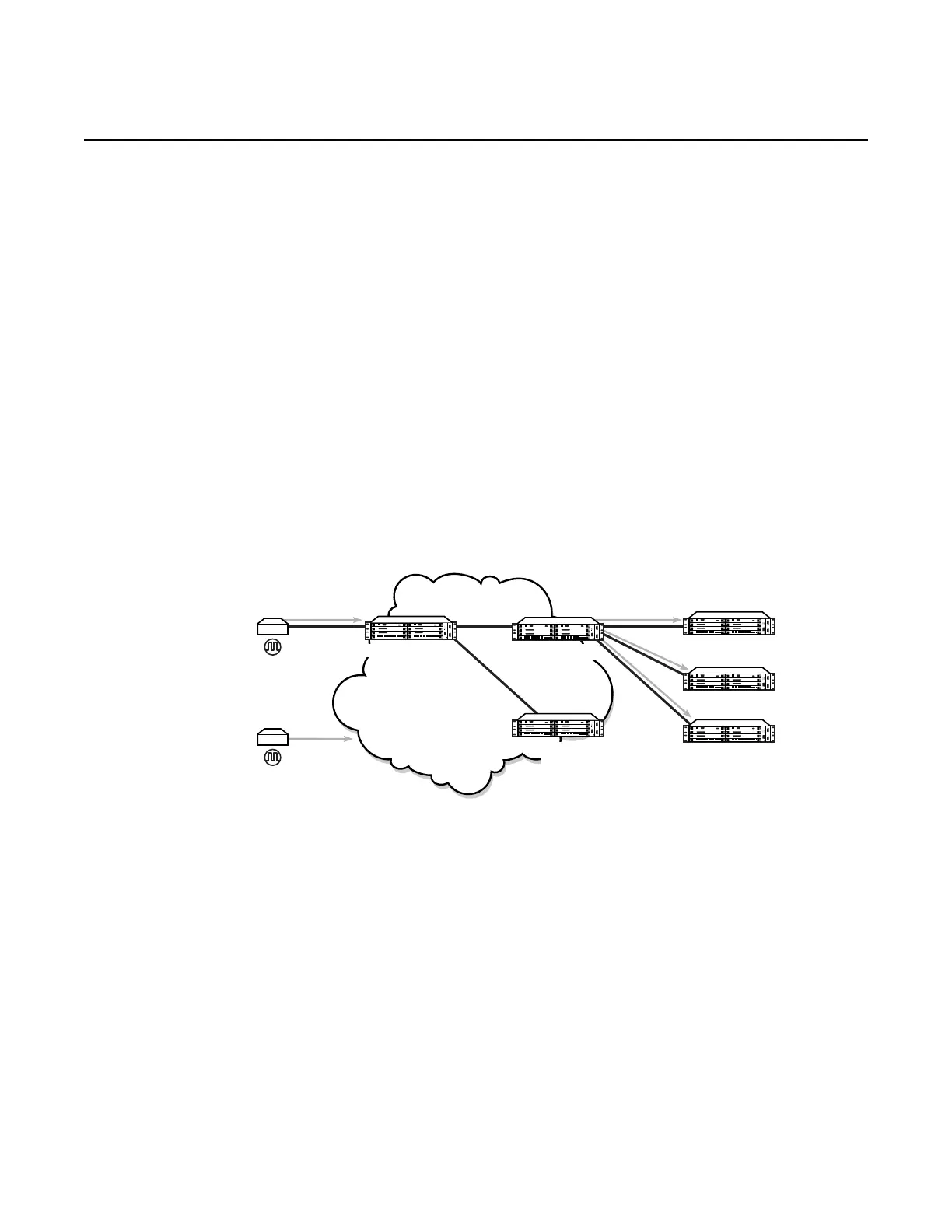

6.4.6.6 PTP Boundary Clock For Frequency

The 7705 SAR supports boundary clock PTP devices in both master and slave

states. IEEE 1588v2 can function across a packet network that is not PTP-aware;

however, the performance may be unsatisfactory and unpredictable. PDV across the

packet network varies with the number of hops, link speeds, usage rates, and the

inherent behavior of the routers. By using routers with boundary clock functionality in

the path between the grand master clock and the slave clock, one long path over

many hops is split into multiple shorter segments, allowing better PDV control and

improved slave performance. This allows PTP to function as a valid timing option in

more network deployments and allows for better scalability and increased

robustness in certain topologies, such as rings.

Boundary clocks can simultaneously function as a PTP slave of an upstream grand

master (ordinary clock) or boundary clock, and as a PTP master of downstream

slaves (ordinary clock) and/or boundary clocks. Figure 20 shows the operation of a

boundary clock.

Figure 20 Boundary Clock

The PTP boundary clock capability is implemented on the Ethernet ports of the

platforms listed in Table 25 and on the cards listed in Table 26.

The 7705 SAR-8 can support up to six boundary clocks and the 7705 SAR-18 can

support up to eight boundary clocks. The fixed platforms listed in Table 25 can each

support one boundary clock.

Packet

Network

1588v2

Grand

Master

1588v2

Grand

Master

21308

PTP Slave

PTP Slave

PTP Slave

PTP Boundary

Clock

PTP Boundary

Clock

PTP Boundary

Clock

Loading...

Loading...