174

Basic Ladder Diagrams Section 4-3

tus of IR 00004 and the second time for an AND with the inverse of the status

of IR 00005.

TR bits can be used as many times as required as long as the same TR bit is

not used more than once in the same instruction block. Here, a new instruc-

tion block is begun each time execution returns to the bus bar. If, in a single

instruction block, it is necessary to have more than eight branching points that

require the execution condition be saved, interlocks (which are described

next) must be used.

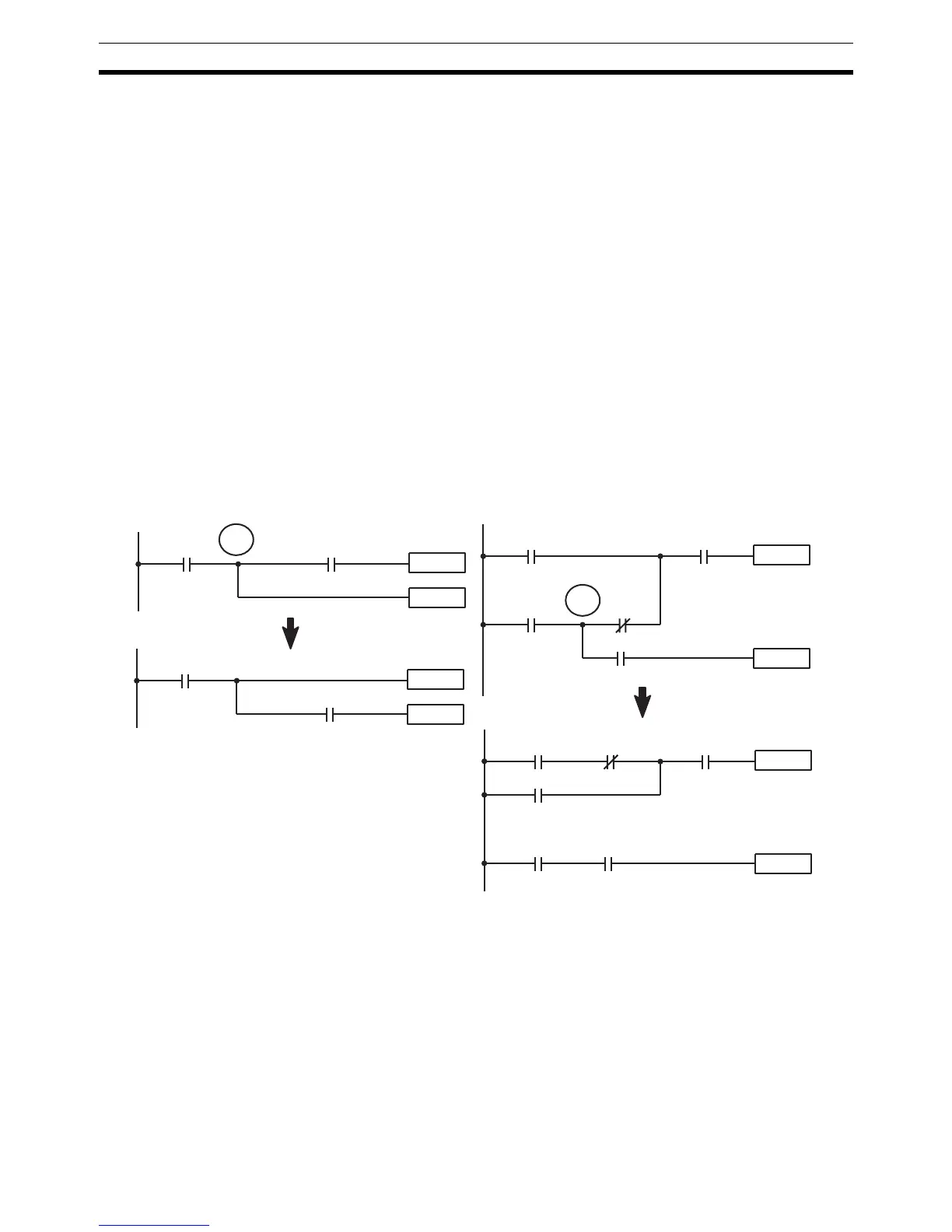

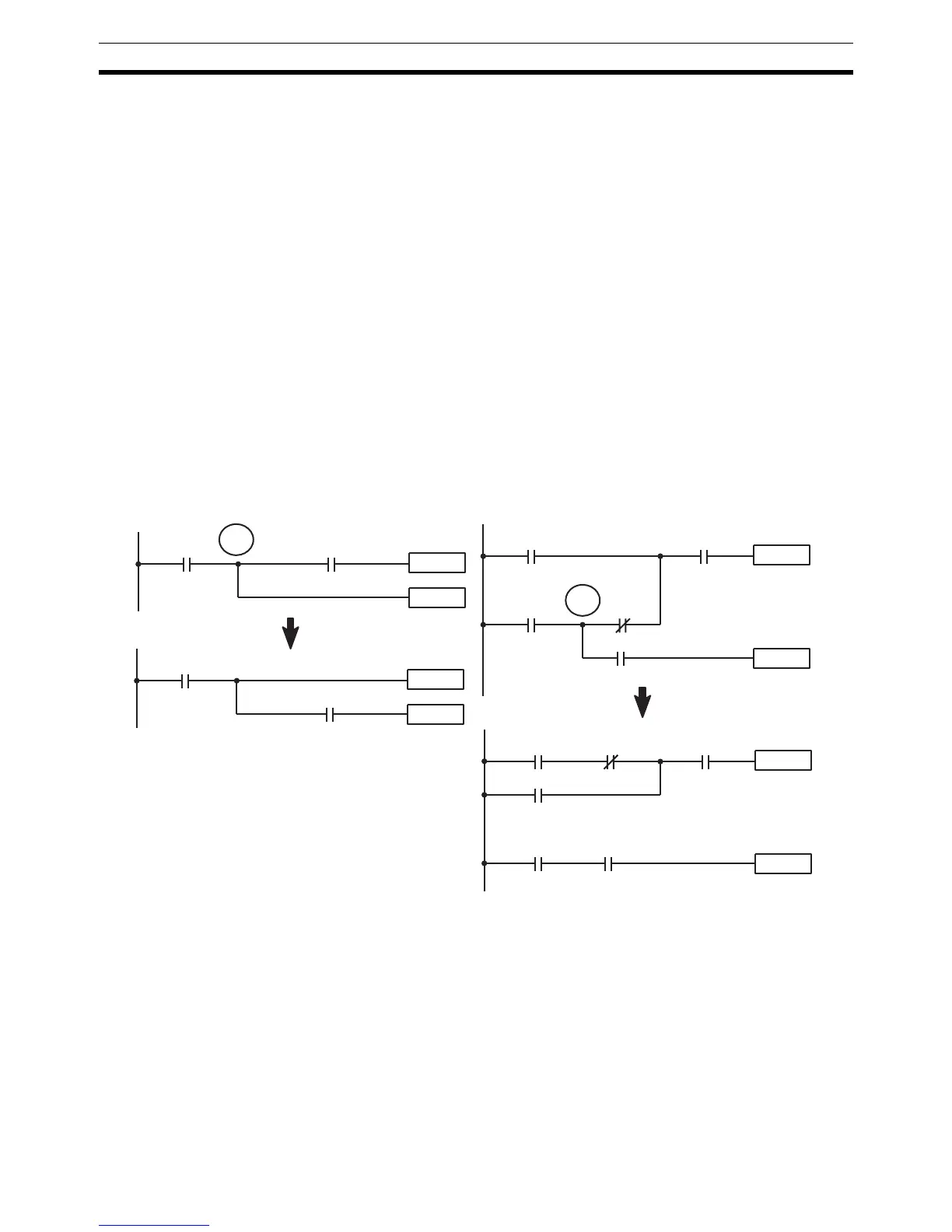

When drawing a ladder diagram, be careful not to use TR bits unless neces-

sary. Often the number of instructions required for a program can be reduced

and ease of understanding a program increased by redrawing a diagram that

would otherwise required TR bits. In both of the following pairs of diagrams,

the bottom versions require fewer instructions and do not require TR bits. In

the first example, this is achieved by reorganizing the parts of the instruction

block: the bottom one, by separating the second OUTPUT instruction and

using another LOAD instruction to create the proper execution condition for it.

Note Although simplifying programs is always a concern, the order of execution of

instructions is sometimes important. For example, a MOVE instruction may be

required before the execution of a BINARY ADD instruction to place the

proper data in the required operand word. Be sure that you have considered

execution order before reorganizing a program to simplify it.

Note TR bits are must be input by the user only when programming using mne-

monic code. They are not necessary when inputting ladder diagrams directly

because they are processed for you automatically. The above limitations on

the number of branching points requiring TR bits, and considerations on

methods to reduce the number of programming instructions, still hold.

Interlocks The problem of storing execution conditions at branching points can also be

handled by using the INTERLOCK (IL(02)) and INTERLOCK CLEAR

(ILC(03)) instructions to eliminate the branching point completely while allow-

ing a specific execution condition to control a group of instructions. The

INTERLOCK and INTERLOCK CLEAR instructions are always used together.

Instruction 1

00000

Instruction 2

00001

TR 0

Instruction 2

00000

Instruction 1

00001

Instruction 1

00000

Instruction 2

00003

TR 0

00001

00004

00002

00001 00003

00000

00004

00002

00001

Instruction 1

Instruction 2

Loading...

Loading...