1

1

2

2

3

3

4

4

5

5

6

6

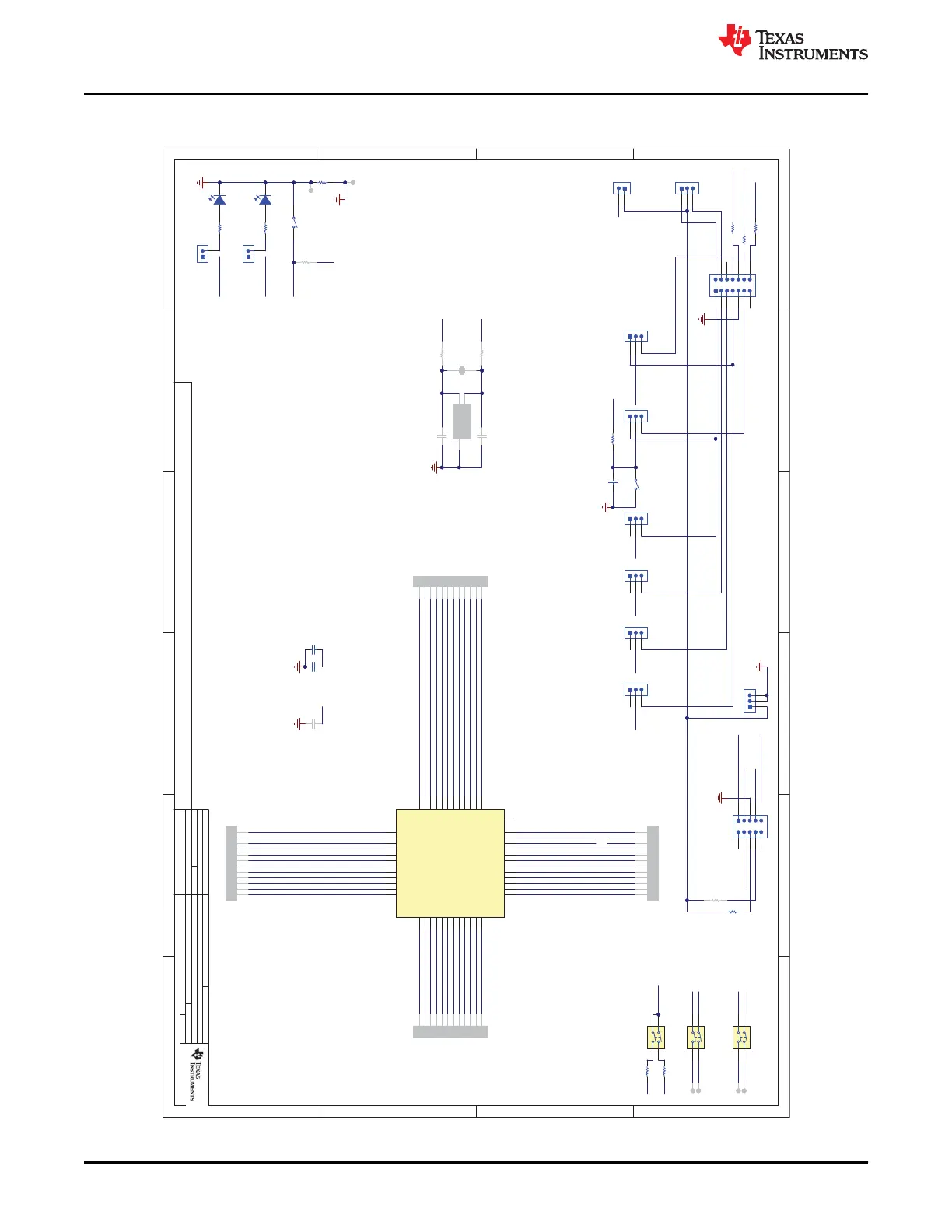

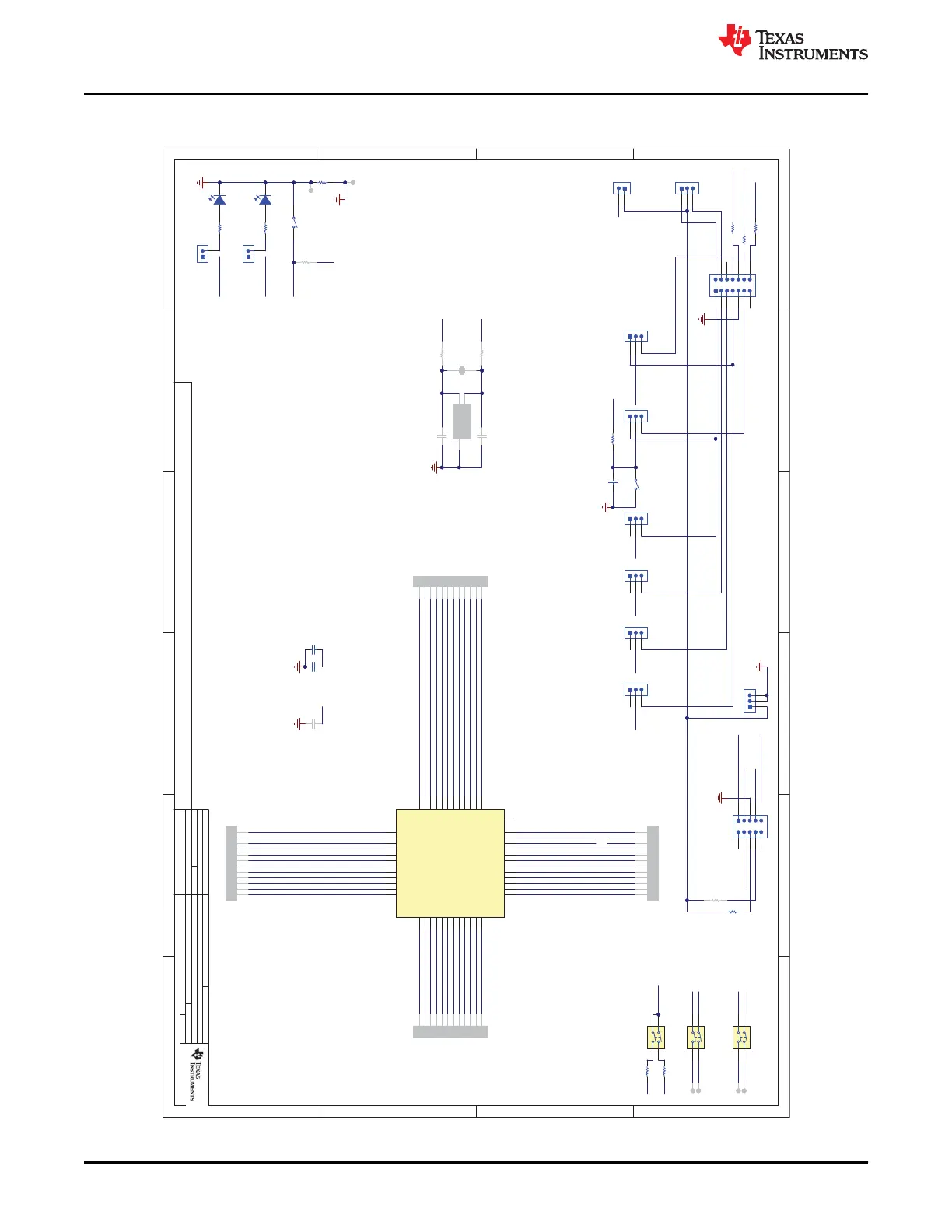

D D

C C

B B

A A

1 2

9/12/2018

MCU046A_Schematic.SchDoc

Sheet Title:

Size:

Mod. Date:

File:

Sheet: of

B

http://www.ti.com

Contact:

http://www.ti.com/support

MSP-TS430PT48AProject Title:

Designed for: Public Release

Assembly Variant: 001

© Texas Instruments 2018

Drawn By:

Engineer:

M Pridgen

Texas Instruments and/or its licensors do not warrant the accuracy or completeness of this specification or any information containedtherein. Texas Instruments and/or its licensors do not

warrant that this design will meet the specifications, will be suitable for your application or fit for any particular purpose, or will operate in an implementation. Texas Instruments and/or its

licensors do not warrant that the design is production worthy. You should completely validate and test your design implementation to confirm the system functionality for your application.

Version control disabledSVN Rev:

MCU046Number: Rev: A

TID #: N/A

Orderable: MSP-TS430PT48A

ext

int

VCC

JTAG ->

SBW ->

TEST/SBWTCK1

TEST/SBWTCK

GND

RST/SBWTDIO P1.7/TDO P1.6/TDI P1.5/TMS P1.4/TCK

DVSS

TMS

TDI

TDO/SBWTDIO

VCC

GND

GND

TEST/SBWTCK

BSL_RX

BSL_TX

DVSS

P1.0

P4.7

DVCC

P4.0

GND

RST/SBWTDIO

BSL_SCL

BSL_SDA

UART BSL Connection

I2C Pullups

BSLRX

BSLTX BSL_TX

BSL_RX

BSLSCL

BSLSDA BSL_SDA

BSL_SCL

DVCC

VCC Current

Measurement

DVCC

BSLSDA

BSLSCL

BSL_TX

BSL_RX

BSL_SDA

BSL_SCL

RST/NMI

TCK/SBWTCK

Ext_PWR

I2C BSL Connection

VCC

DVCC

DVSS

P1.4/TCK

P1.5/UCA0RXD/UCA0SOMI/TA1.1/TMS/A5P1.5/TMS

P1.4/UCA0TXD/UCA0SIMO/TA1.2/TCK/A4/VREF+

P1.7/TDO P1.7/UCA0STE/SMCLK/TDO/A7

P1.6/UCA0CLK/TA1CLK/TDI/TCLK/A6P1.6/TDI

P5.3/UCB1CLK/TA3.0/A10

P5.4/UCB1STE/TA3CLK/A11

P1.0/UCB0STE/TA0CLK/A0/Veref+

RST/NMI/SBWTDIO

DVCC

DVSS

HFGND Connection by viaXOUT_ext

XIN_ext

P4.4/UCB1SIMO/UCB1SDA/TB0.6/A9

TEST/SBWTCK

RST/SBWTDIO

DVCC

DVCC

X1 on hardware page is included loose in the kit

and is intended to be populated on Q1B as needed

P1.1/UCB0CLK/TA0.1/COMP0.0/A1

P1.2/UCB0SIMO/UCB0SDA/TA0.2/A2/Veref-

P1.3/UCB0SOMI/UCB0SCL/MCLK/A3

P2.2/ACLK/COMP0.1

P4.5/UCB0SOMI/UCB0SCL/TA3.2

P4.6/UCB0SIMO/UCB0SDA/TA3.1

P5.5/UCB0CLK/TA2CLK

P5.6/UCB0STE/TA2.0

P5.7/TA2.1/COMP0.2

P6.0/TA2.2/COMP0.3

P3.0/TA2.2

P3.3/TA2.1

TEST/SBWTCK

P2.7/UCB1STE

P4.2/TA3CLK

P4.1/TA3.0

P4.0/TA3.1

P3.7/TA3.2

DNC

P2.6/UCA1TXD/UCA1SIMO

P2.5/UCA1RXD/UCA1SOMI

P2.4/UCA1CLK

P3.1/UCA1STE

P3.4/TA2CLK/COMP0OUT

P2.3/TA2.0

DVSS

P2.1/XIN

P2.0/XOUT

P5.2/UCA0TXD/UCA0SIMO /TB0.4

P5.1/UCA0RXD/UCA0SOMI/TB0.3

P5.0/UCA0CLK/TB0.2

P4.7/UCA0STE/TB0.1

P6.2/TB0.0

P6.1/TB0CLK

P3.6/UCB1SOMI/UCB1SCL

P3.2/UCB1SIMO/UCB1SDA

P3.5/UCB1CLK/TB0TRG

If external supply voltage:

remove R3 and add R4 (0 ohm)

and the I2C BSL and the I2C pull-ups are disconnected

By default the UART BSL is connected

XOUT

XIN

SW2

SW1

12pF

C8

DNP

12pF

C9

DNP

1

2

GND

3

32.768kHz

Q1B

DNP

P4.3/UCB1SOMI/UCB1SCL/TB0.5/A8

P1.0

XIN

XOUT

XIN_ext

XOUT_ext

DVSS

P4.0

1 2

3 4

5 6

7 8

9 10

BSL

1100pF

C5

10uF

C7

Green

D1

Blue

D2

1

2

3

J1

1

2

3

J2

1

2

3

JP5

1

2

3

JP6

1

2

3

JP7

1

2

3

JP8

1

2

3

JP9

1

2

3

JP10

5

4

1

2

3

6

7

8

9

10

11

12

J3

DNP

5

4

1

2

3

6

7

8

9

10

11

12

J4

DNP

5

4

1

2

3

6

7

8

9

10

11

12

J5

DNP

5

4

1

2

3

6

7

8

9

10

11

12

J6

DNP

JP1

JP11

JP12

12

34

56

78

910

1112

1314

JTAG

Q1A

DNP

330

R1

200

R2

0

R3

0

R4

DNP

47k

R7

0

R8

DNP

0

R9

DNP

0

R10

47k

R13

DNP

4.7k

R16

4.7k

R17

0

R19

0

R20

0

R21

1 2

3 4

SW3

1 2

3 4

SW4

1 2

3 4

SW5

TP1

DNP

TP2

DNP

TP3

DNP

TP4

DNP

TP5

DNP

TP6

DNP

48

14

45

17

42

20

39

23

26

29

32

35

15

16

46

47

43

44

21

22

40

41

37

38

25

28

31

30

34

36

27

33

11

8

5

2

13

18

19

24

12

9

6

7

3

1

10

4

49

IC1

1uF

C10

DNP

DNC

DVSS

BSLRX

BSLTX

BSLSCL

BSLSDA

P4.7

Customer Note

Populate either Q1A (High Speed) or

Q1B (Low Speed, 32.768KHz) crystal

Customer Note CONN1-4 and CONN5-8 are male and female headers included loose

in the kit and are intended to be populated on J3-6 as needed

Customer Note

0.1uF

C6

Figure B-38. MSP-TS430PT48A Target Socket Module, Schematic

Loading...

Loading...