Chapter 9 Deployment CPU 21xSER-1 Manual VIPA CPU 21x

9-12 HB103E - Rev. 05/45

Velocity of data transfer in Bit/s (Baud).

01h: 150 Baud 05h: 1800 Baud 09h: 9600 Baud 0Dh: 57600 Baud

02h: 300 Baud 06h: 2400 Baud 0Ah: 14400 Baud 0Eh: 115200 Baud

03h: 600 Baud 07h: 4800 Baud 0Bh: 19200 Baud

04h: 1200 Baud 08h: 7200 Baud 0Ch: 38400 Baud

Number of data bits where a character is mapped to.

0: 5Bit 1: 6Bit 2: 7Bit 3: 8Bit

Supported values:

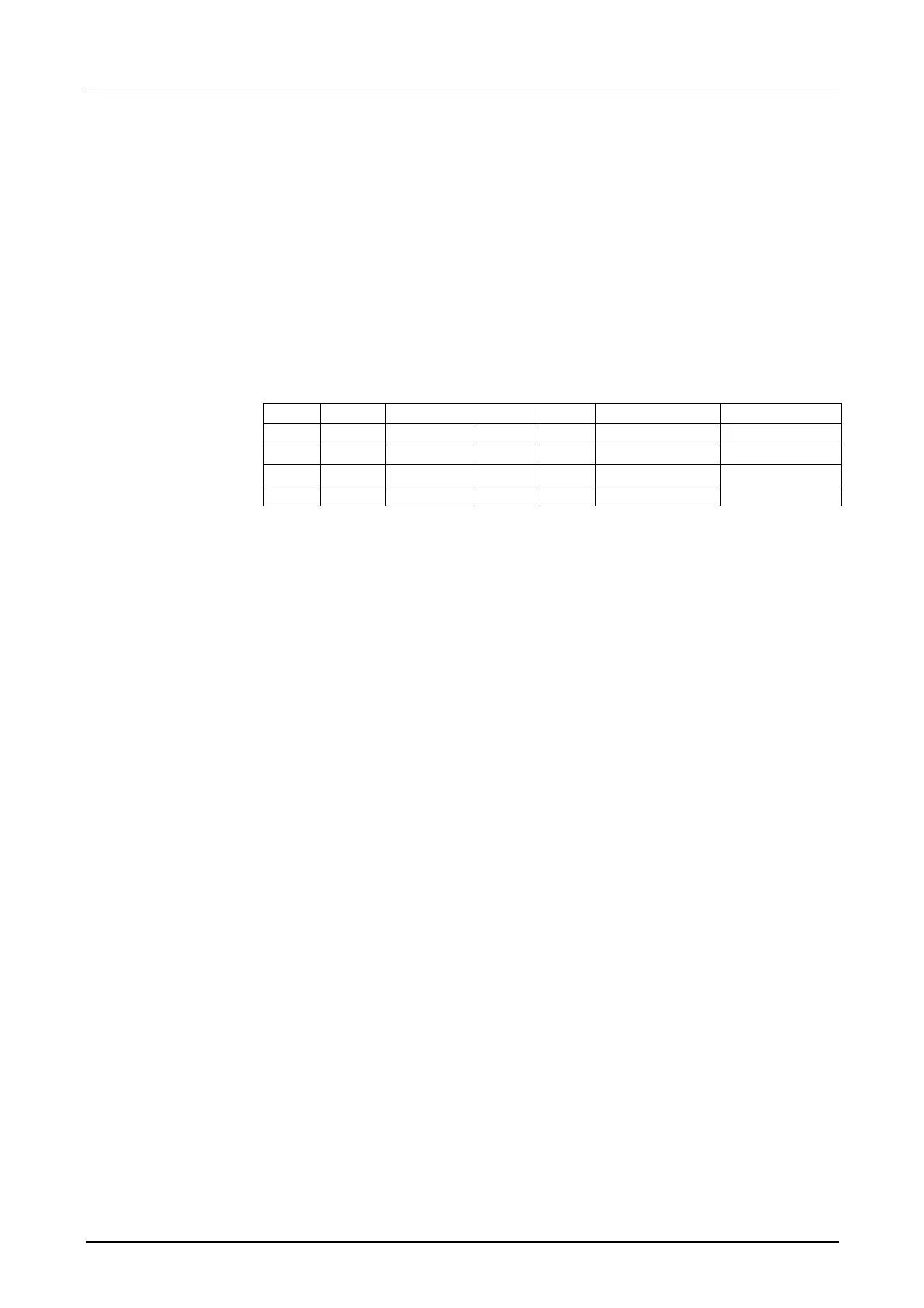

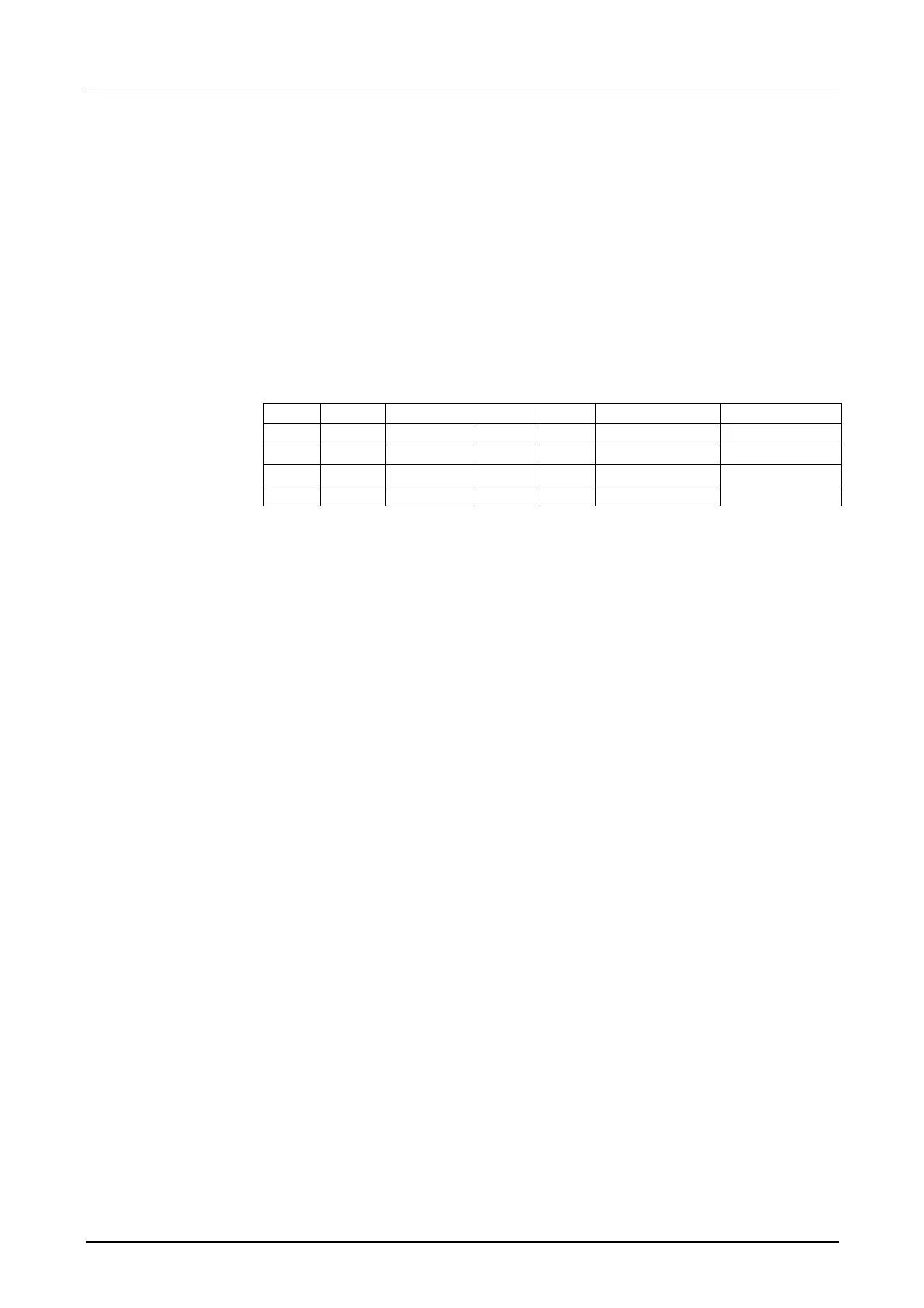

Bit ASCII STX/ETX 3964R USS Modbus RTU Modbus ASCII

5 x x

6 x x x

7 x x x x

8 x x x x x x

The parity is -depending on the value- even or odd. For parity control, the

information bits are extended with the parity bit, that amends via its value

("0" or "1") the value of all bits to a defined status. If no parity is set, the

parity bit is set to "1", but not evaluated.

0: NONE 1: ODD 2: EVEN

The stop bits are set at the end of each transferred character and mark the

end of a character.

1: 1Bit 2: 1.5Bit 3: 2Bit

1.5Bit can only be used with CharLen 5 at this number of data 2Bit is not

allowed.

With this bit you affect the behavior from signal Request to send

"0" = RTS off

"1" = RTS is "0" at Receive

RTS is "1" at Send

Note: For RS485 FlowControl must be "1" !

Baud rate

CharLen

Parity

StopBits

FlowControl

Loading...

Loading...