Depending upon the type

of

addressing, the

reference

address

of

the

PSS

instruction

is

converted

into an

effective

virtual doubleword address, as

described

under "PSS Address

Calculations",

in

Chapter

2. Except for the Register Block

Pointer

field

(bit positions

56-59)

and

the

interrupt

group

inhibit

bits (bit positions

37,

38,

and 39), the contents

of

the

effective

location

are

always loaded as

the

new

PSWs.

If the

lP

flag (bit 8

of

the

PSS

instruction) is a 1, the

Register

Block Pointer

of

the new

PSWs

is

also loaded. If

the

lP

flag

is

a

0,

the old Register Block

Pointerisretained.

The

interrupt

group

inhibit

bits

of

the

new

PSWs

are

1I0Red

ll

with the corresponding bits

of

the

old

PSWs.

The

current

environment (comprised

of

20 words) is stored

in

memory

stack

locations having

the

following

relative

addresses:

initial

TSA+1

through

initial

TSA+16,

initial

TSA+25,

and

initial

TSA+26. Memory

stack

locations

having

ref-ative addresses

of

initial

TSA+17 through

initial

TSA+24,

initial

TSA+27, and

initial

TSA+28

are

reserved

and

the

contents

are

indeterminate.

The parameters

of

the Status

Stack

Pointer Doubleword (as

contained

within working registers)

are

appropriately

mod-

ified

to

reflect

the progress

of

the

PSS

instruction and

conditions

of

the memory

stack

(i.

e.,

the

TSA

and Word

Count

are

incremented

and the Space

Count

is

decremented

for

each

memory word

location

accessed,

as described under

Status

Stack

Pointer Doubleword).

If

the

Word Count

exceeds

32,767

(maximum count for

bits

49-63)

or

if

the Space

Count

is reduced to zero before

the

PSS

instruction is completed, the

stacking

operations

continue

unti I 28 words

have

been

pushed (i.

e.,

no trapping

occurs). When the Word

Count

exceeds

32,767,

bit

48

is

set

to a

1.

Attempting to

decrement

the

Space

Count below

zero

causes

the

Space

Count

to become

indeterminate.

Affected:

(PSWs), CC, Memory

Stack,

Status Stack Pointer

Doubleword.

(PSWs)

and CC:

EDO_3-CC;

ED4-7-

FR,

FS,

FZ, FN;

ED8-MS;

ED9-MM;

ED10-DMi

ED11-AMi

ED15-31

-IAi

ED32-35-WK;

ED37-39 u CI,

II,

EI

- CI, II,

EI

(Note:

"u

ll

represents inclusive OR. )

ED

56

-

59

-

RP

on

Iy

if

(I8) = 1

E

D

60-

RA

ED61-MA

104 Push-Down Instructions (Privileged)

Memory Stack:

(General

Register n) - (initial TSA+(n+l) where n has

ascending

values from 0 through 15.

PSW1

- (initial TSA+25)

PSW2

- (initial TSA+26)

Status

Stack

Pointer Doubleword:

TSA+1

-

TSA

unti I terminal TSA=initial

TSA+28i

Word Count + 1 - Word

Count

unti I terminal Word

Count

=

initial

Word Count + 28, (if Word

Count>

32,767,

set

bit

48

to 1);

Space Count - 1 - Space Count unti I terminal Space

Count =

initial

Space Count - 28 (if Space Count = 0,

Space

Count

- 1

is

indeterminate).

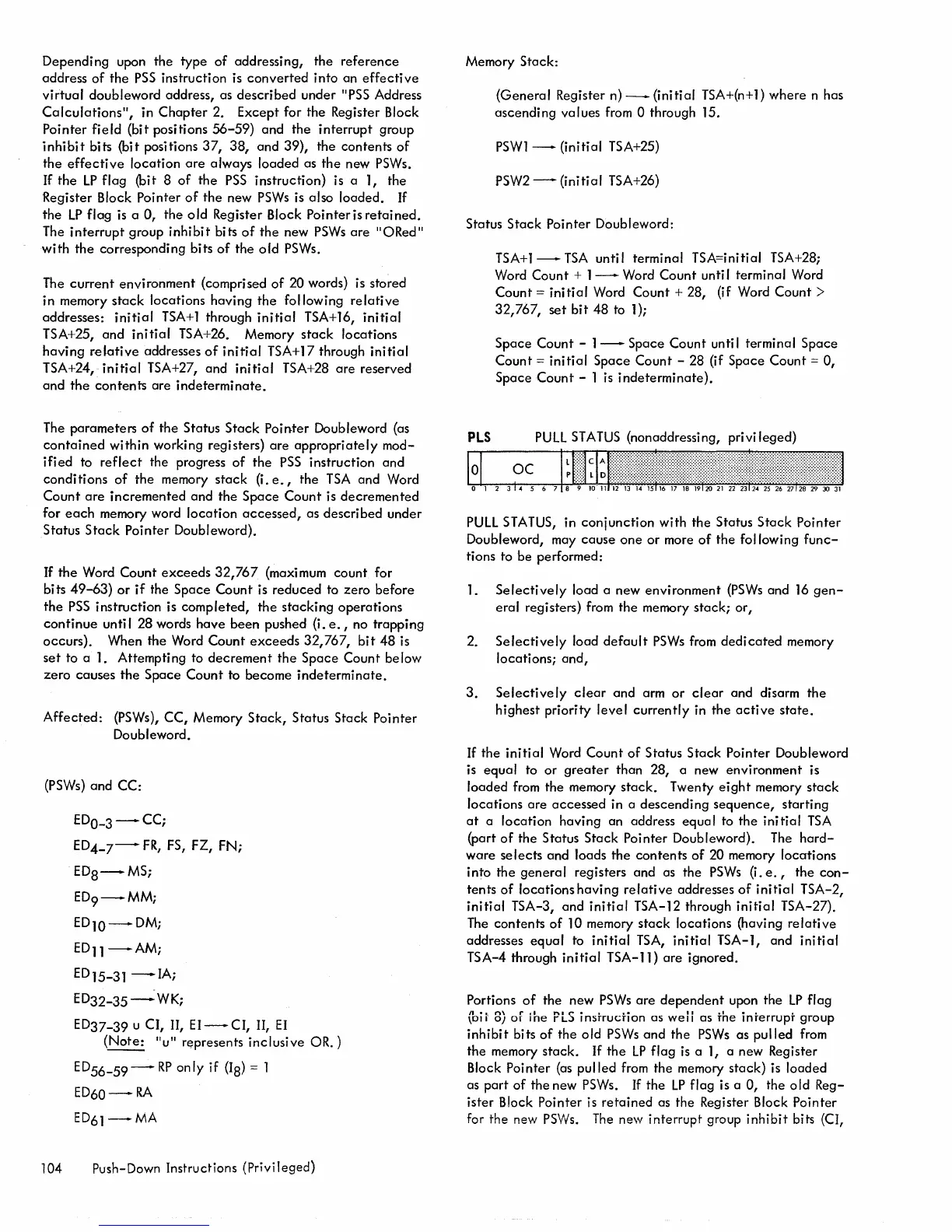

PLS

PULL

STATUS

(nonaddressing,

privileged)

PULL

STATUS,

in

conjunction

with the Status

Stack

Pointer

Doubleword, may cause

one

or

more

of

the following

func-

tions to be performed:

1.

Selectively

load a new environment

(PSWs

and

16

gen-

eral registers) from

the

memory

stack;

or,

2.

Selectively

load

default

PSWs

from

dedicated

memory

locations;

and,

3.

Selectively

clear

and arm

or

clear

and disarm the

highest priority

level

currently

in

the

active

state.

If the

initial

Word Count

of

Status

Stack

Pointer Doubleword

is

equal to or

greater

than 28, a new environment is

loaded from the memory

stack.

Twenty

eight

memory

stack

locations

are

accessed in a descending

sequence,

starting

at

a location having an address equal to the

initial

TSA

(part

of

the Status

Stack

Pointer Doubleword). The

hard-

ware

selects

and loads the

contents

of

20 memory locations

into the

general

registers and as the

PSWs

(i. e., the

con-

tents

of

locations having

relative

addresses

of

initial

TSA-2,

initial

TSA-3, and

initial

TSA-12 through

initial

TSA-27).

The

contents

of

10

memory

stack

locations (having

relative

addresses

equal

to

initial

TSA,

initial

TSA-l,

and

initial

TSA-4 through

initial

TSA-11)

are

ignored.

Portions

of

the new

PSWs

are

dependent

upon the

LP

flag

II-Ln\

r~t

nlr-

I.-

11.1...

\011

OJ

or

me

fL.)

JnsrruclJon as well as

me

mTerrupT

group

inhibit

bits

of

the old

PSWs

and

the

PSWs

as pulled

from

the memory

stack.

If the

LP

flag

is

a 1, a new Register

Block Pointer

(as

pulled from the memory stack) is loaded

as

part

of

the new

PSWs.

If

the

LP

flag is a 0, the old Reg-

ister Block

Pointer is

retained

as the Register Block Pointer

for the new

PSWs.

The

new interrupt group

inhibit

bits (CI,

Loading...

Loading...