The

XPSD

instruction'

is

used for

three

distinct

types

of

operations:

as a norma I instruction in an ongoing program;

as

an

interrupt

instruction;

and

as a

trap

instruction.

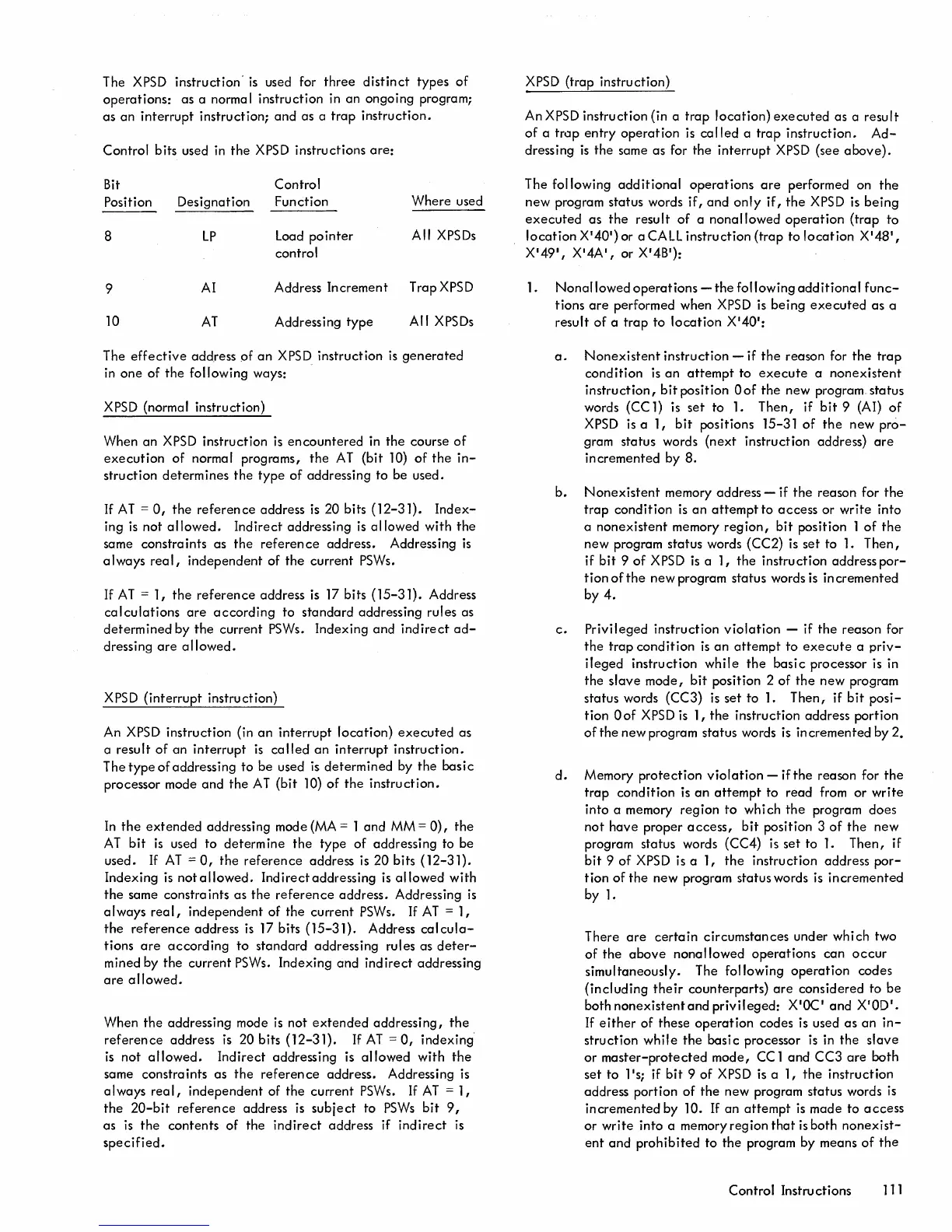

Control bits used

in

the

XPSD

instructions

are:

Bit

Position

8

9

10

Designation

LP

AI

AT

Control

Function

Load

pointer

control

Where used

All XPSDs

Address

Increment

Trap

XPSD

Address i ng

type

A I I X

PS

Ds

The

effective

address

of

an

XPSD instruction

is

generated

in

one

of

the

following ways:

XPSD

(normal instruction)

When

an

XPSD

instruction

is

encountered

in

the

course

of

execution

of

normal programs,

the

AT

(bit 10)

of

the

in-

struction

determines

the

type

of

addressing

to

be used.

If

AT

=

0,

the

reference

address

is

20 bits

(12-31).

Index-

ing

is

not

allowed.

Indirect

addressing

is

allowed

with

the

same constraints as

the

reference

address. Addressing

is

always

real,

independent

of

the

current

PSWs.

If

AT

= 1,

the

reference

address is

17

bits

(15-31).

Address

calculations

are

according

to

standard

addressing rules as

determined

by

the

current

PSWs. Indexing and

indirect

ad-

dressing

are

allowed.

XPSD

(interrupt

instruction)

An

XPSD

instruction (in

an

interrupt

location)

executed

as

a result

of

an

interrupt

is

called

an

interrupt

instruction.

The

type

of

addressing

to

be used

is

determined

by

the

basic

processor mode and

the

AT

(bit 10)

of

the

instruction.

In

the

extended

addressing mode (MA = 1 and

MM

=

0),

the

AT

bit

is

used

to

determine

the

type

of

addressing to be

used.

If

AT

=

0,

the

reference

address is 20 bits {12-31}.

Indexing

is

not

allowed.

Indirectaddressing

is

allowed

with

the

same constraints as

the

reference

address. Addressing

is

always

real,

independent

of

the

current

PSWs.

If

AT

= 1,

the

reference

address

is

17 bits

(15-31).

Address

calcula-

tions

are

according

to

standard addressing rules as

deter-

mined by

the

current

PSWs.

Indexing and

indirect

addressing

are

allowed.

When

the

addressing mode

is

not

extended

addressing,

the

reference

address

is

20 bits

(l2-31).

If

AT

=

0,

indexing·

is

not

allowed.

Indirect

addressing is

allowed

with

the

same constraints as

the

reference

address. Addressing

is

always

real,

independent

of

the

current

PSWs.

If

AT

= 1,

the

20-bit

reference

address is

subject

to

PSWs

bit

9,

as

is

the

contents

of

the

indirect

address if

indirect

is

specified.

XPSD

(trap instruction)

An

XPSD

instruction (in a

trap

location)

executed

as a

result

of

a

trap

entry

operation

is

called

a

trap

instruction.

Ad-

dressing

is

the

same as for

the

interrupt

XPSD

(see

above).

The fol lowing

additional

operations

are

performed on

the

new

program status words

if,

and

only

if I

the

XPSD

is

being

executed

as

the

result

of

a

nonallowed

operation

(trap

to

location

X'40')

or a CALL instruction

(trap

to

location

X'48',

X'49',

X'4A',

or X'4B'):

1.

Nonal

lowed

operations

-

the

fol lowing

additional

func-

tions

are

performed when

XPSD

is

being

executed

as

a

result

of

a

trap

to

location

X'40':

a.

Nonexistent

instruction - if

the

reason for

the

trap

condition

is

an

attempt

to

execute

a

nonexistent

instruction,

bit

position Oof

the

new program status

words

(CC

1)

is

set

to

1.

Then,

if

bit

9 (AI)

of

XPSD

is

a 1,

bit

positions 15-31

of

the

new

pro-

gram status words

(next

instruction address)

are

incremented

by

8.

b.

Nonexistent

memory address - if

the

reason for

the

trap

condition

is

an

attempt

to

access

or

write

into

a

nonexistent

memory

region,

bit

position 1

of

the

new program status words (CC2) is

set

to

1.

Then,

if

bit

9

of

XPSD

is

a

1,

the

instruction address

por-

tion

of

the

new program status words is

in

cremented

by

4.

c.

Privileged instruction

violation

- if

the

reason for

the

trap

condition

is

an

attempt

to

execute

a

priv-

ileged

instruction

while

the

basic

processor is in

the

slave

mode,

bit

position 2

of

the

new program

status words (CC3) is

set

to

1.

Then,

if

bit

posi-

tion

Oof

XPSD

is

1,

the

instruction address portion

of

the

new program

status

words is

incremented

by 2.

d.

Memory

protection

violation

-

ifthe

reason for

the

trap

condition

is

an

attempt

to

read

from

or

write

into

a memory region

to

which

the

program does

not

have

proper

access,

bit

position 3

of

the

new

program status words (CC4) is

set

to

1.

Then,

if

bit

9

of

XPSD

is a 1,

the

instruction address

por-

tion

of

the

new program status words is

incremented

by

1.

There

are

certain

circumstances under which two

of

the

above

nonal lowed

operations

can

occur

simultaneously. The following

operation

codes

(including

their

counterparts)

are

considered to

be

both

nonexistent

and

privileged:

X'QC'

and

X'OD'.

If

either

of

these

operation

codes is used

as

an

in-

struction

while

the

basi c processor is in

the

slave

or

master-protected

mode,

CC

1

and

CC3

are

both

set

to

l's;

if

bit

9

of

XPSD

is

a 1,

the

instruction

address portion

of

the

new program status words

is

incremented

by 10.

If

an

attempt

is

made

to

access

or

write

into a memory region

that

is

both

nonexist-

ent

and

prohibited

to

the

program by means

of

the

Control Instructions

111

Loading...

Loading...