MicroBlaze Processor Reference Guide 172

UG984 (v2018.2) June 21, 2018 www.xilinx.com

Chapter 3: MicroBlaze Signal Interface Description

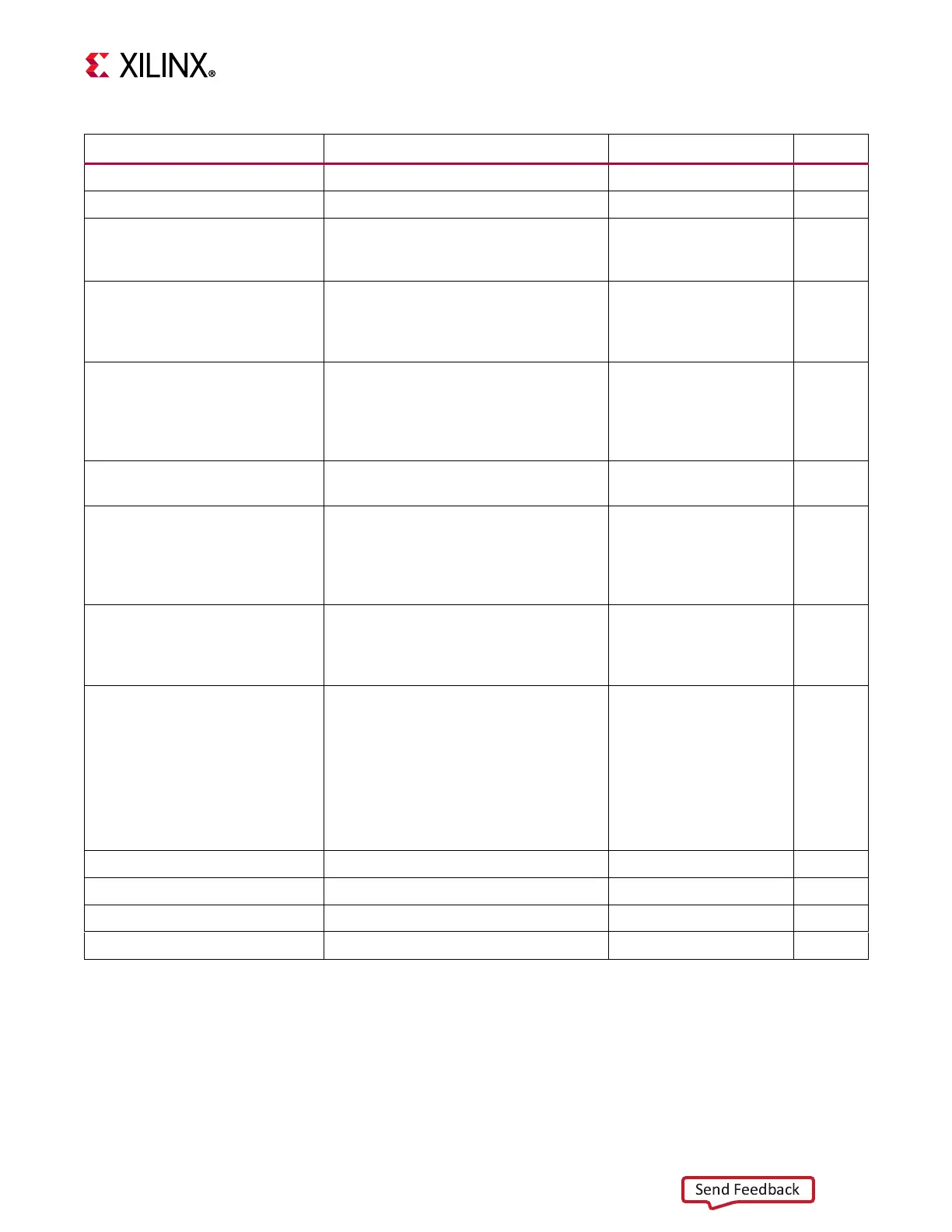

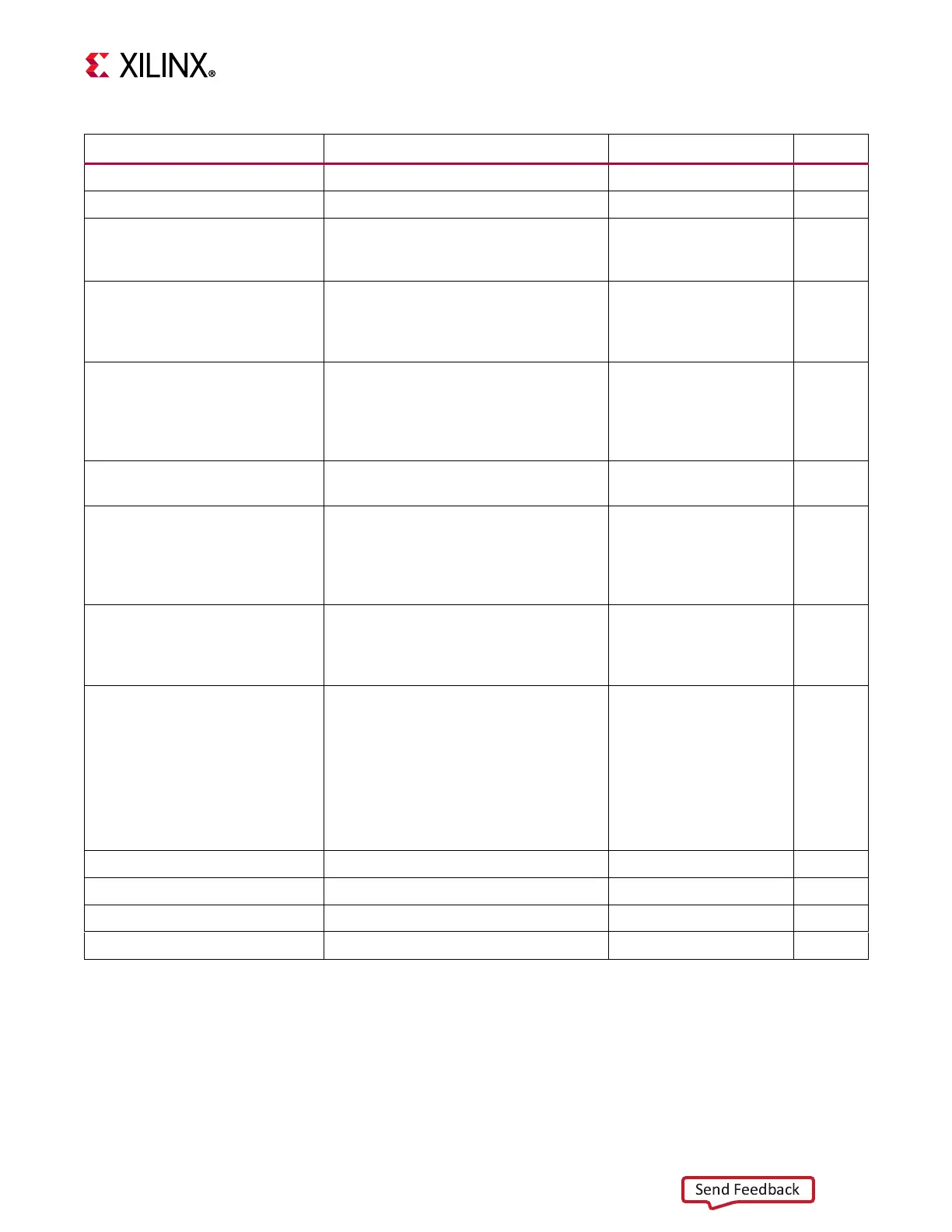

Trace_Data_Read

1

D-side memory access is a read

std_logic

output

Trace_Data_Write

1

D-side memory access is a write

std_logic

output

Trace_DCache_Req Data memory address is within

D-Cache range. Set when a memory

access instruction is executed.

std_logic

output

Trace_DCache_Hit Data memory address is present in

D-Cache. Set simultaneously with

Trace_DCache_Req when a cache hit

occurs.

std_logic

output

Trace_DCache_Rdy Data memory address is within

D-Cache range and the access is

completed. Only set following a request

with Trace_DCache_Req = 1 and

Trace_DCache_Hit = 0.

std_logic

output

Trace_DCache_Read The D-Cache request is a read. Valid

only when Trace_DCache_Req = 1.

std_logic

output

Trace_ICache_Req Instruction memory address is within

I-Cache range, and the cache is enabled

in the Machine Status Register. Set

when an instruction is read into the

instruction prefetch buffer.

std_logic

output

Trace_ICache_Hit Instruction memory address is present

in I-Cache. Set simultaneously with

Trace_ICache_Req when a cache hit

occurs.

std_logic

output

Trace_ICache_Rdy

• Instruction memory address is present

in I-Cache. Set simultaneously with

Trace_ICache_Req when a cache hit

occurs in this case.

• Instruction memory address is within

I-Cache range and the access is

completed. Set following a request

with Trace_ICache_Req = 1 and

Trace_ICache_Hit = 0 in this case.

std_logic

output

Trace_OF_PipeRun Pipeline advance for Decode stage

std_logic

output

Trace_EX_PipeRun

3

Pipeline advance for Execution stage

std_logic

output

Trace_MEM_PipeRun

3

Pipeline advance for Memory stage

std_logic

output

Trace_MB_Halted Pipeline is halted by debug

std_logic

output

1. Valid only when Trace_Valid_Instr = 1

2. Valid only when

Trace_Exception_Taken = 1

3. Not used with area optimization feature

Table 3-16: MicroBlaze Trace Signals (Cont’d)

Signal Name Description VHDL Type Direction

Loading...

Loading...