MIPI CSI-2 RX Subsystem v4.0 79

PG232 July 02, 2019 www.xilinx.com

Appendix A: Verification, Compliance, and Interoperability

information on MIPI IOB compliant solution and guidance, refer D-PHY Solutions (XAPP894)

[Ref 15].

A series of interoperability test scenarios listed in Tab le A-2 and Tabl e A-3 are validated

using different core configurations and resolutions. All ZCU102 designs use the native MIPI

IO available in the UltraScale+ FPGA.

All Xilinx 7 series FPGA interop designs use the external Meticom (MC20901) based solution

which implements MIPI D-PHY IO.

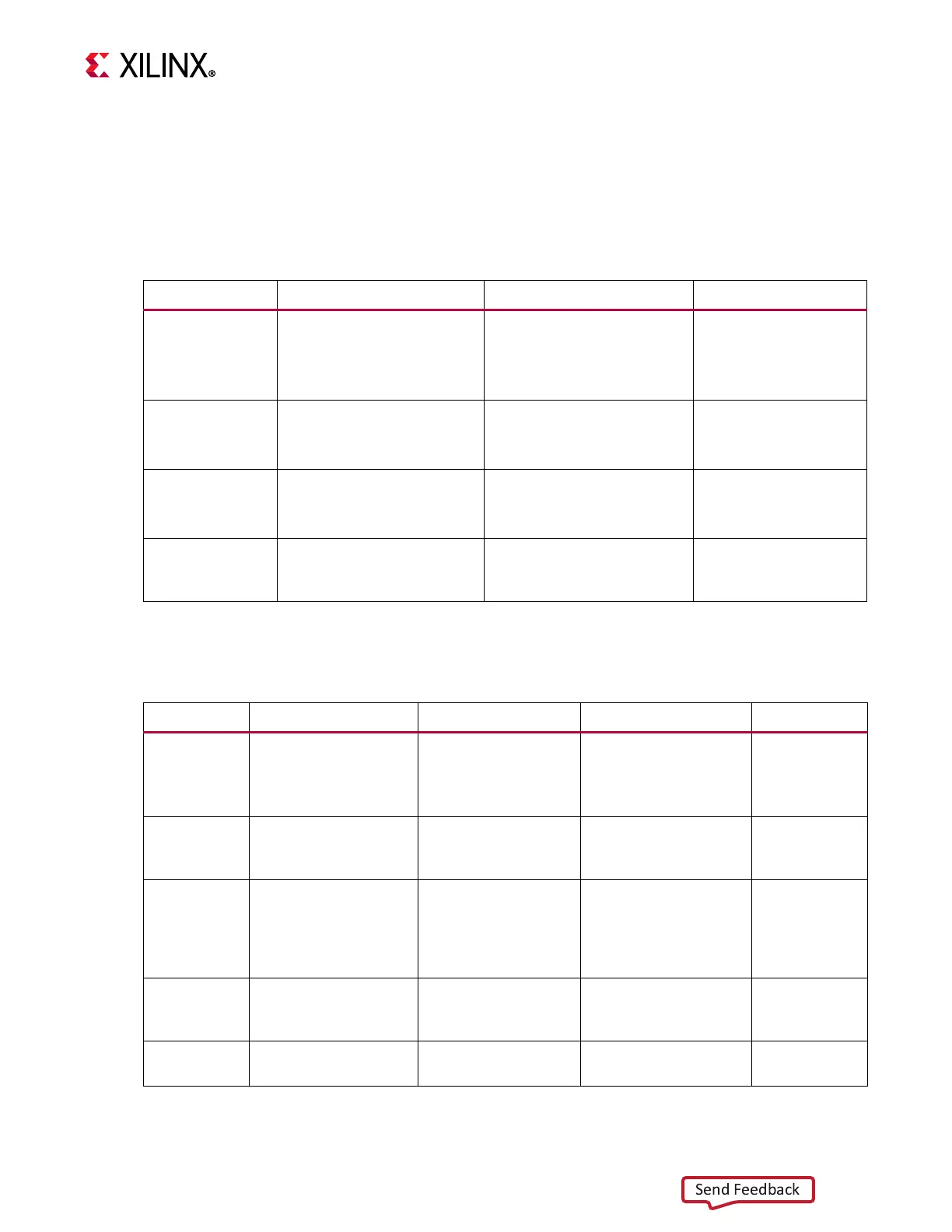

Table A-2: Interoperability Testing UltraScale+ Device

Sensor Board/Device Tested Configuration Resolution

Omnivision

OV13850

ZCU102/

xczu9eg-ffvb1156-2-e

1200Mb/s 1, 2, 4 Lanes

RAW8, RAW10, RAW12

480p@60fps

720p@60fps

1080p@60fps

4k@30fps

Sony IMX274

ZCU102/

xczu9eg-ffvb1156-2-e

1440Mb/s

4 Lanes

RAW10, RAW12

All supported modes

by sensor

Sony IMX224

ZCU102/

xczu9eg-ffvb1156-2-e

149Mb/s, 594Mb/s

1, 2, 4 Lanes

RAW10, RAW12

All-pixel (QVGA) and

Window cropping

modes

ON Semi AR0330

ZCU102/

xczu9eg-ffvb1156-2-e

490Mb/s 4 Lanes RAW10

480p@60fps

720p@60fps

1080p@60fps

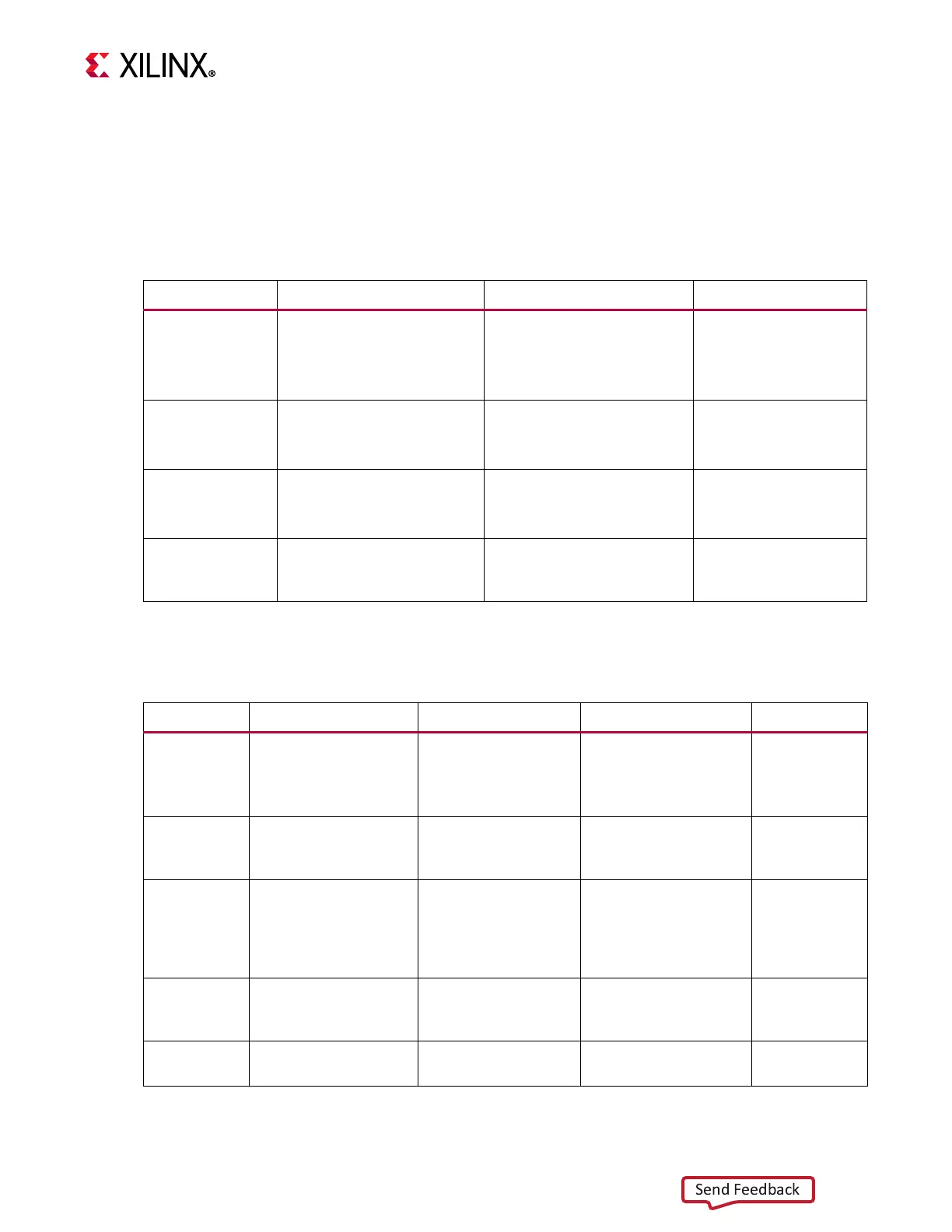

Table A-3: Interoperability Testing with Xilinx 7 Series FPGA Devices

Sensor Board/Device Tested Configuration Calibration Mode Resolution

Sony IMX274

ZC702/

xc7z020clg484-1

576Mb/s 4 Lanes

RAW10

Auto Enable 300 MHz

clock for

IDELAYCTRL=false

1080p@60fps

Sony IMX274

ZC702/

xc7z020clg484-1

1152Mb/s 2 Lanes

RAW10

Auto Enable 300 MHz

clock for

IDELAYCTRL=true

1080p@60fps

ON Semi

AR0330

KC705/

xc7k325tffg900-2

490Mb/s 4 Lanes

RAW10

None

480p@60fps

720p@60fps

1080p@60fps

2304x1296@6

0fps

ON Semi

AR0330

KC705/

xc7k325tffg900-2

588Mb/s 4 Lanes

RAW12

None

1080p@60fps

2304x1296@6

0fps

ON Semi

AR0330

ZC702/

xc7z020clg484-1

490Mb/s 4 Lanes

RAW10

None 480p@60fps

Loading...

Loading...