MC97F6108A User’s manual 6. Interrupt controller

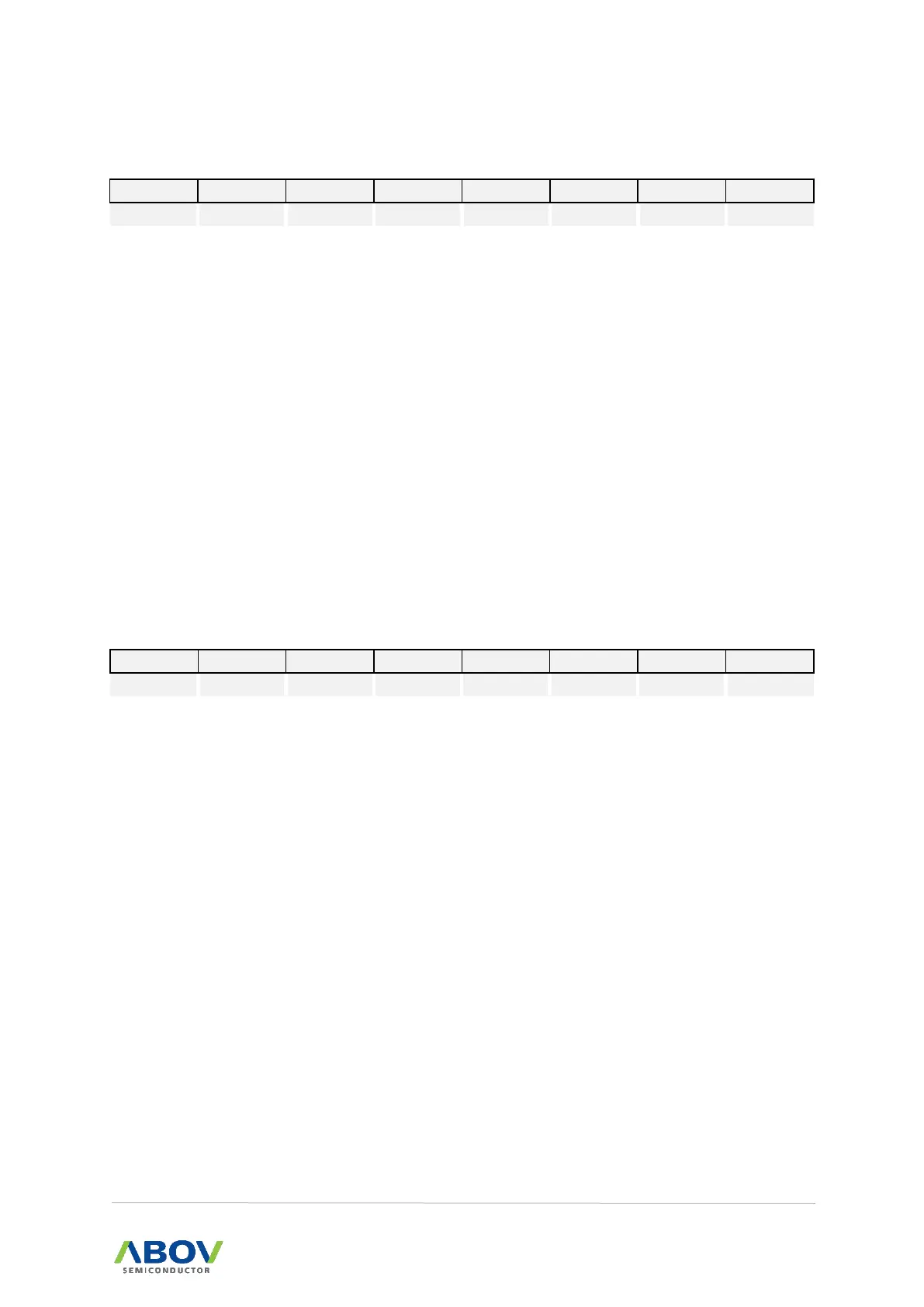

EIFLAG (External Interrupt Flag0 Register): A4H

When a PCI interrupt or an External Interrupt 0-2 are occurred while

EIENAB is set to ‘1’, the flag becomes ‘1’.The flag is cleared only by

writing ‘0’ to the bit. It is also cleared automatically before interrupt

service routine is served.

When Pin Change Interrupt occurs this bit is set.

Pin Change Interrupt not occurred

Pin Change Interrupt occurred

When External Interrupt 2 occurs this bit is set.

External Interrupt2 not occurred

External Interrupt2 occurred

When External Interrupt 1 occurs this bit is set.

External Interrupt1 not occurred

External Interrupt1 occurred

When External Interrupt 0 occurs this bit is set.

External Interrupt0 not occurred

External Interrupt0 occurred

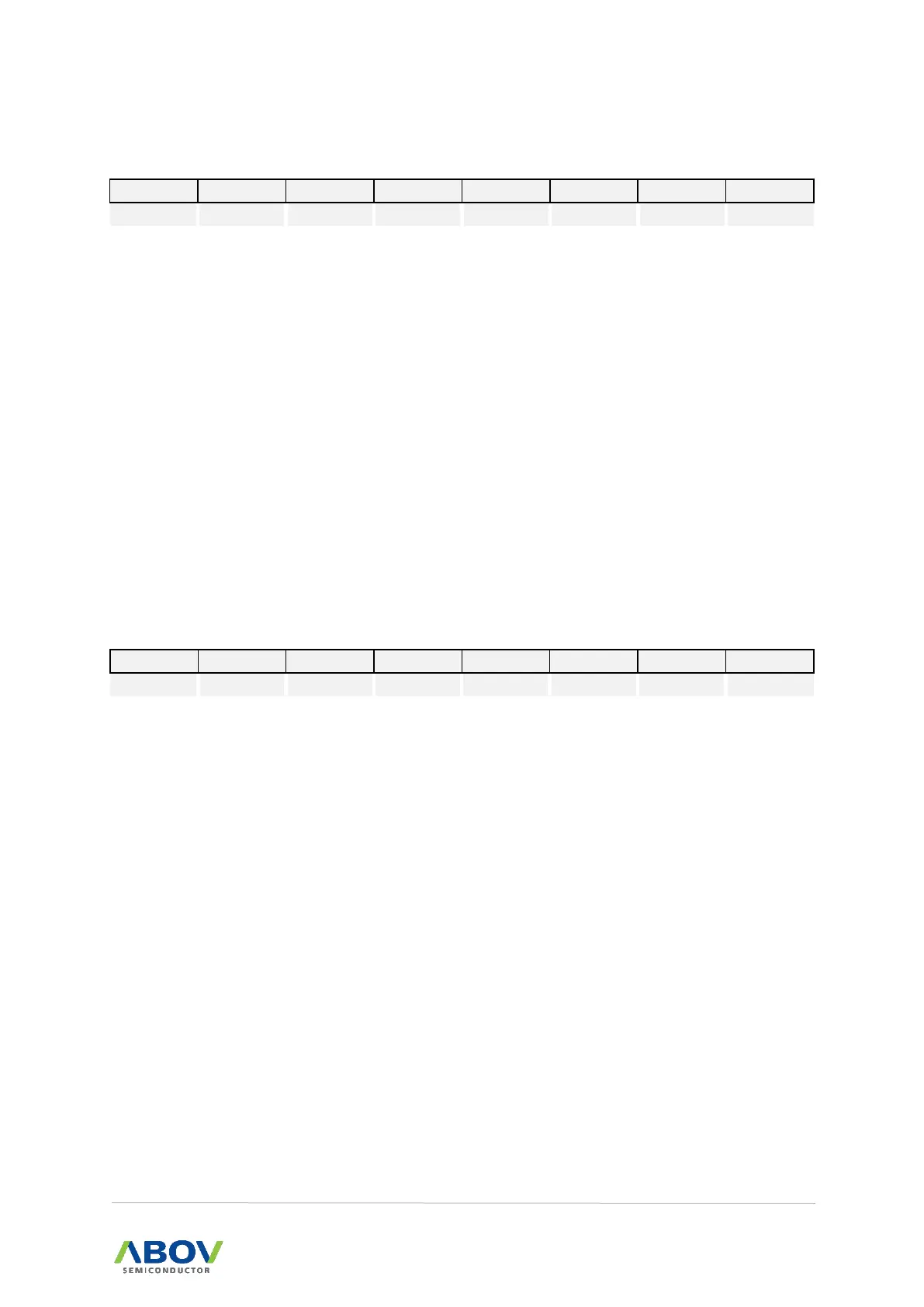

EIEDGE (External Interrupt Flag Edge Register) : A5H

Determines the type of External interrupt 2, edge or level sensitive.

Determines the type of External interrupt 1, edge or level sensitive.

Determines the type of External interrupt 0, edge or level sensitive.

Loading...

Loading...