35

7647H–AVR–03/12

Atmel ATmega16/32/64/M1/C1

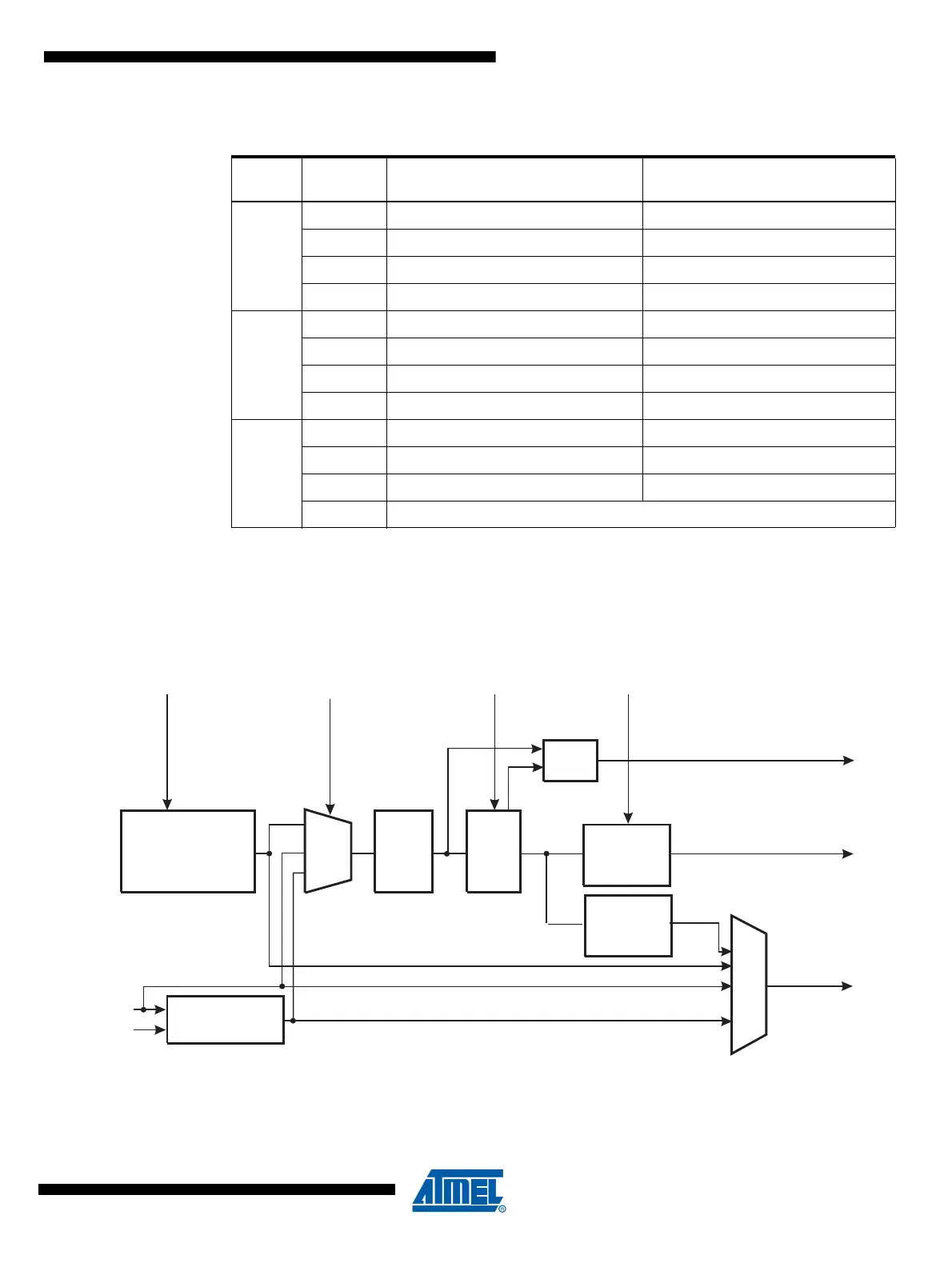

Figure 5-3. PLL Clocking System

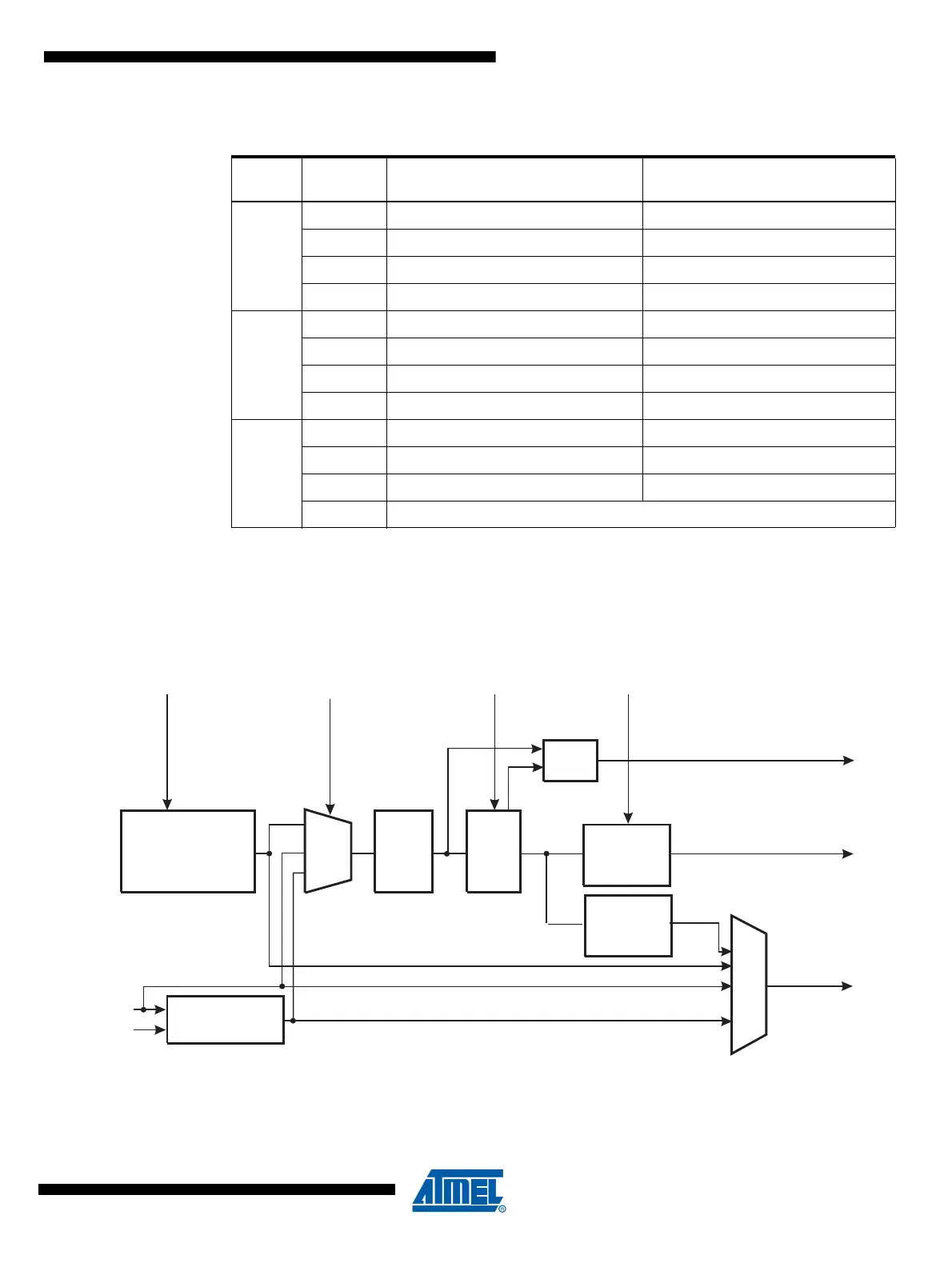

Table 5-7. Start-up Times when the PLL is selected as system clock

CKSEL

3..0 SUT1..0

Start-up Time from Power-down

and Power-save

Additional Delay from Reset

(V

CC

= 5.0V)

0011

RC Osc

00 1K CK 14CK

01 1K CK 14CK + 4 ms

10 1K CK 14CK + 64 ms

11 16K CK 14CK

0101

Ext Osc

00 1K CK 14CK

01 1K CK 14CK + 4 ms

10 16K CK 14CK + 4 ms

11 16K CK 14CK + 64 ms

0001

Ext Clk

00 6 CK

(1)

1. This value do not provide a proper restart ; do not use PD in this clock scheme

14CK

01 6 CK

(2)

2. This value do not provide a proper restart ; do not use PD in this clock scheme

14CK + 4 ms

10 6 CK

(3)

3. This value do not provide a proper restart ; do not use PD in this clock scheme

14CK + 64 ms

11 Reserved

8 MHz

RC OSCILLATOR

OSCCAL

XTAL1

XTAL2

OSCILLATORS

DIVIDE

BY 8

DIVIDE

BY 2

CK

PLL

64x

PLLE

Lock

Detector

PLOCK

SOURCE

PLLF

DIVIDE

BY 4

CLK

PLL

CKSEL3..0

Loading...

Loading...