Test Setup - Test Configurator, Timer, and System

MaxTester 169

Signal - Signal Configuration (DSn/PDH)

Modify DS0/E0

Modify DS0/E0 button is only available when the DS0/E0 check box is

selected.

Note: For DS0, the framing structure has 24 timeslots. For E0, the framing

structures PCM-30 and PCM30 CRC-4 have 30 channel timeslots (1 to 15

and 17 to 31) while PCM-31 and PCM-31 CRC-4 have 31 channel timeslots

(1 to 31).

DS0/E0 Size sets the channel timeslot data rate for the pattern payload

content to either 56K or 64K (default); forced to respectively 56K for

DS0 and 64K for E0 when TX Signaling is enabled. A timeslot data rate

of 56 Kbit/s uses 7 bits while 64 Kbit/s uses 8 bits to carry the payload

information.

Zero Code Suppression allows the selection of the Zero Code

Suppression (ZCS) method used to replace the all-zero bytes of the Idle

and Tone payload contents. The ZCS mechanism is a global parameter

meaning that all channel timeslots configured with Tone/Idle data, use

the same ZCS method. Choices are:

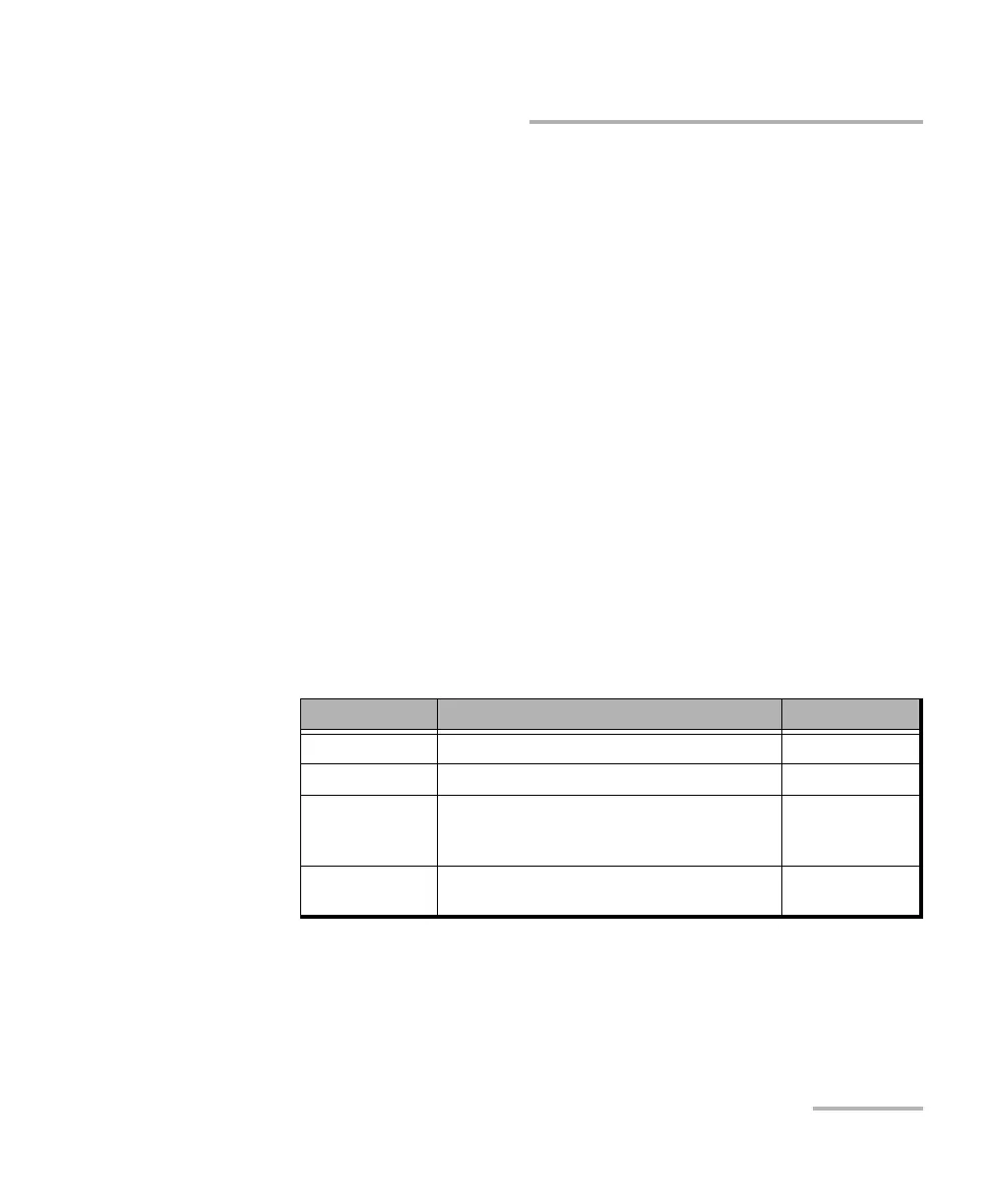

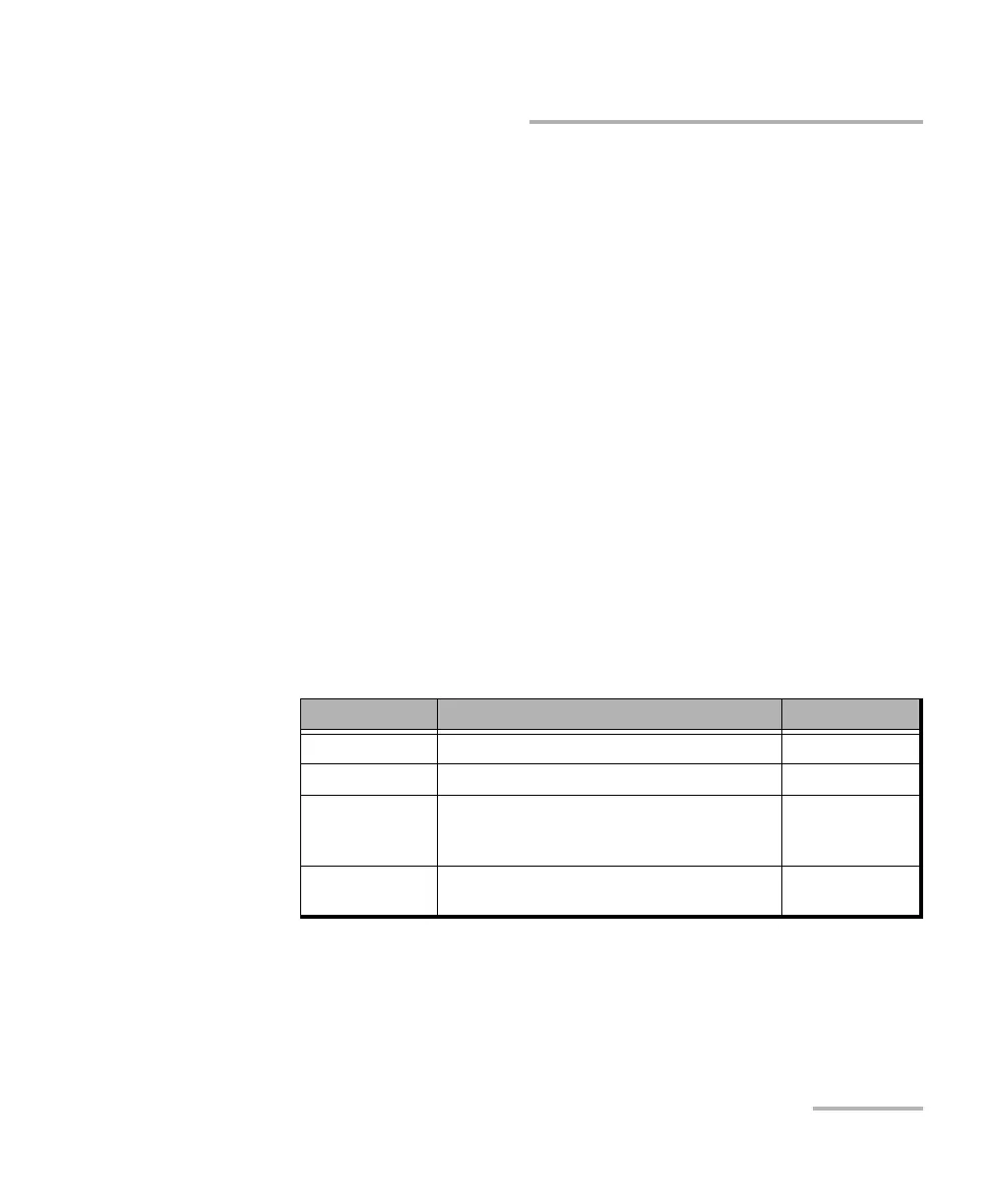

ZCS Description Available with

None

a

a. Default value.

No Zero Code Suppression DS0 and E0

Jammed Bit 8 Every 8th (LSB) bit is forced to 1.DS0 and E0

GTE Bit 8 of an all zero channel byte is replaced

by 1, except in signaling frames where bit 7 is

forced to 1.

DS0

Bell Bit 7 of an all zero channel byte is replaced

by 1.

DS0

Loading...

Loading...