Registers

The status register

is

accessed

by system

reads.

It provides

information

to

the

system about the status

of

the hard disc

controller card.

Two

of

the bits indicate the protocol phase

of

the

controller. The

other

bits

of

this register flag various conditions

such

as:

the

status

of

the last command, when a block

of

data

is

ready

to

be

transferred, and when a command

has

been

completed.

This

status register

can

be

polled

for

programmed

I/O

applications.

The control register

is

a latch

to

which the system writes

to

inform

the

controller when

to

enter different

phases

of

operation.

The data port

is

bidirectional and

passes

not

only data,

but

command and status information also.

To

the system this data

port appears

to

be

a

FIFO.

The

FIFO

arrangement allows the

system

to

read

or

write the data

without

handshaking each byte.

The data register should

be

read

or

written

to

only during the

appropriate command phases.

Memory

HP

Vectra

PC

requires a system

ROM

and

RAM

on the hard disc

subsystem card

for

the disc

BIOS.

These

reside in 8 Kbytes

of

system memory space. The

ROM

occupies the first 6 Kbytes and

the RAM the last 2 Kbytes.

The address

of

this 8 Kbytes block

can

be

selected by the

four

switches on the subsystem card

in

the

COO

00

to

DFOOO

hex range.

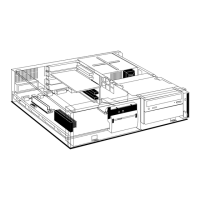

The following figure shows the location

of

the switches on both

the hard disc subsystem cards.

The jumpers are configured

for

the 20 Mbyte hard disc subsystem.

110

Disc Drives

",-."