Clock

Cycle

The HP45981 A operates from the master oscillator at 22.440MHz

and the backplane clock at 14.3818MHz.

Adapter-to-System Hardware

Interface

The HP45981A

is

interfaced

to

the 80286 microprocessor

as

an

8-bit memory device and and 8-bit

I/O

device. All signal lines are

buffered

onto

the card and load

to

the

system bus. Wait-states

are provided

for

memory

accesses

to

synchronize the 80286. The

RAM on the card

is

on four 16 Kbyte x 4 RAM chips.

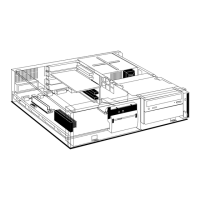

Jumpers and Connectors

The following card layout shows the connectors and jumpers on

the H

P45981

A.

Multi-Mode Video Adapter Card Layout

P3

XXXXXXX

EJ

P1

Figure 19

J2

J1

Multi-Mode Video Adapter Card

81