Intel® Server System M50CYP1UR Family System Integration and Service Guide

102

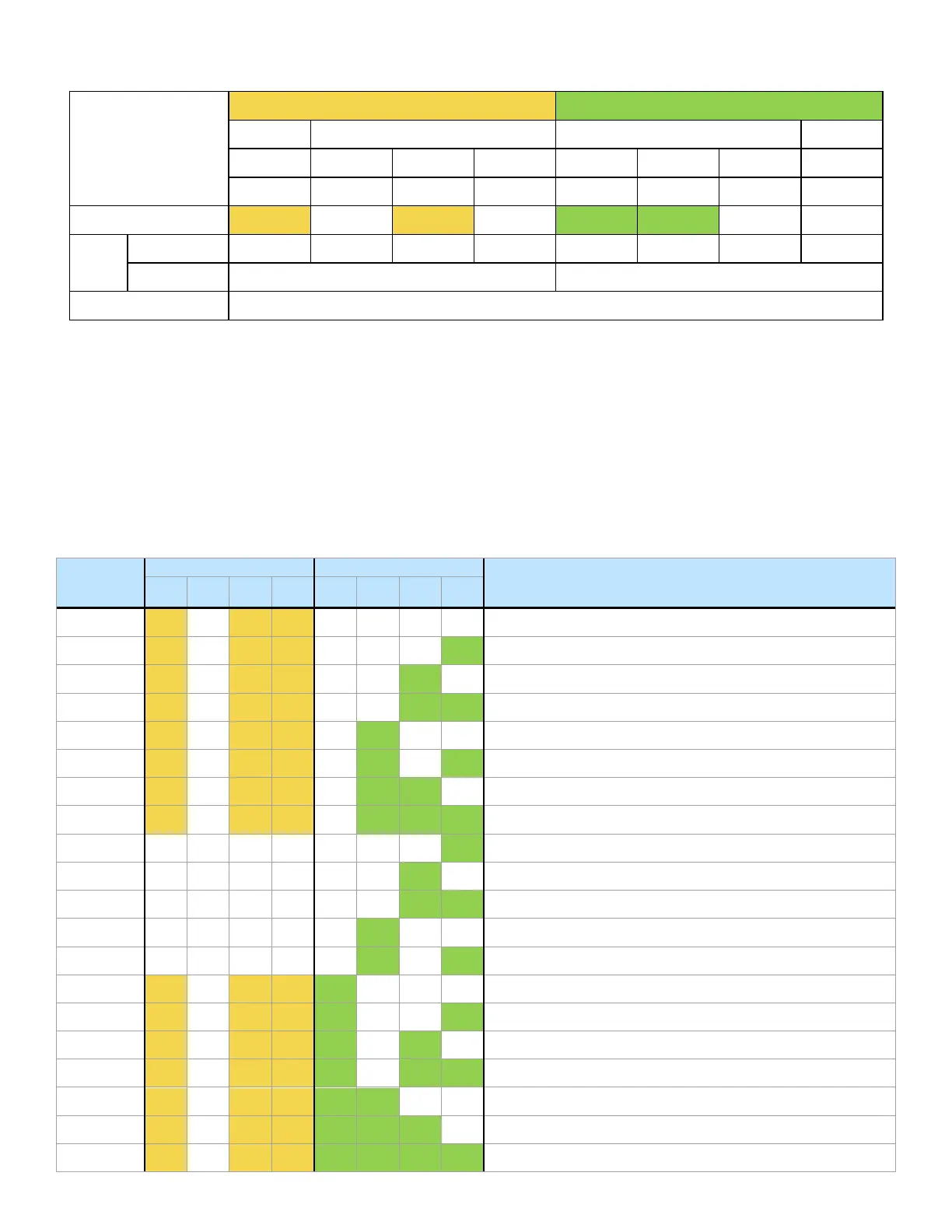

Table 8. POST Progress Code LED Example

Upper nibble bits = 1010b = Ah; Lower nibble bits = 1100b = Ch; the two Hex Nibble values are combined to

create a single ACh POST Progress Code.

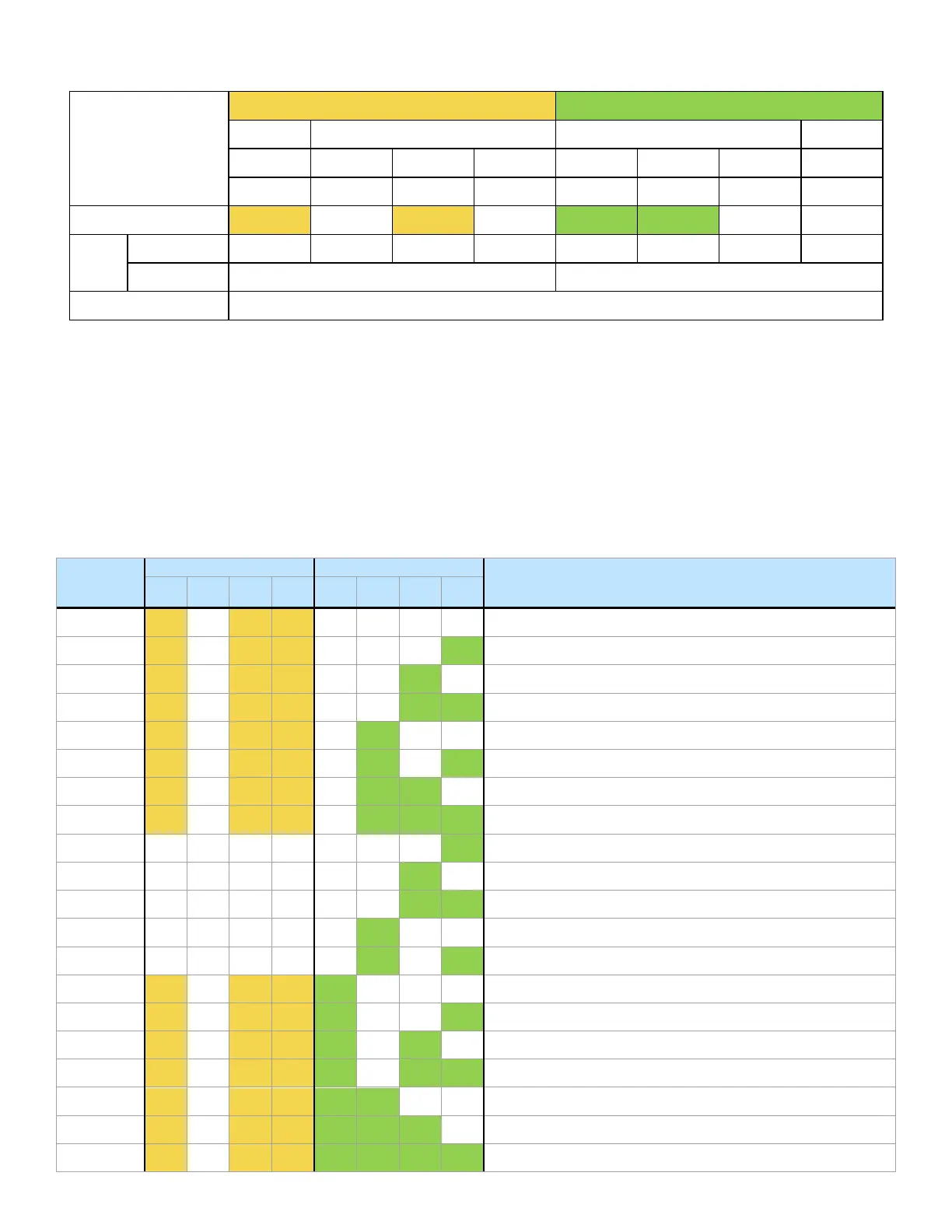

E.1 Early POST Memory Initialization MRC Diagnostic Codes

Memory initialization at the beginning of POST includes multiple functions: discovery, channel training,

validation that the DIMM population is acceptable and functional, initialization of the IMC and other

hardware settings, and initialization of applicable RAS configurations.

The MRC progress codes are displayed to the diagnostic LEDs that show the execution point in the MRC

operational path at each step.

Table 9. MRC Progress Codes

Gather remaining SPD data

Program registers on the memory controller level

Evaluate RAS modes and save rank information

Program registers on the channel level

Perform the JEDEC defined initialization sequence

Train DDR4 ranks – Read DQ/DQS training

Train DDR4 ranks – Receive enable training

Train DDR4 ranks – Write DQ/DQS training

Train DDR4 ranks – DDR channel training done

Hardware memory test and init

Execute software memory init

Program memory map and interleaving

Program RAS configuration

Loading...

Loading...