RH850/F1Kx, RH850/F1K Series Hardware Design Guide

R01AN3841ED0110 Rev. 1.10 Page 64 of 108

August 8, 2019

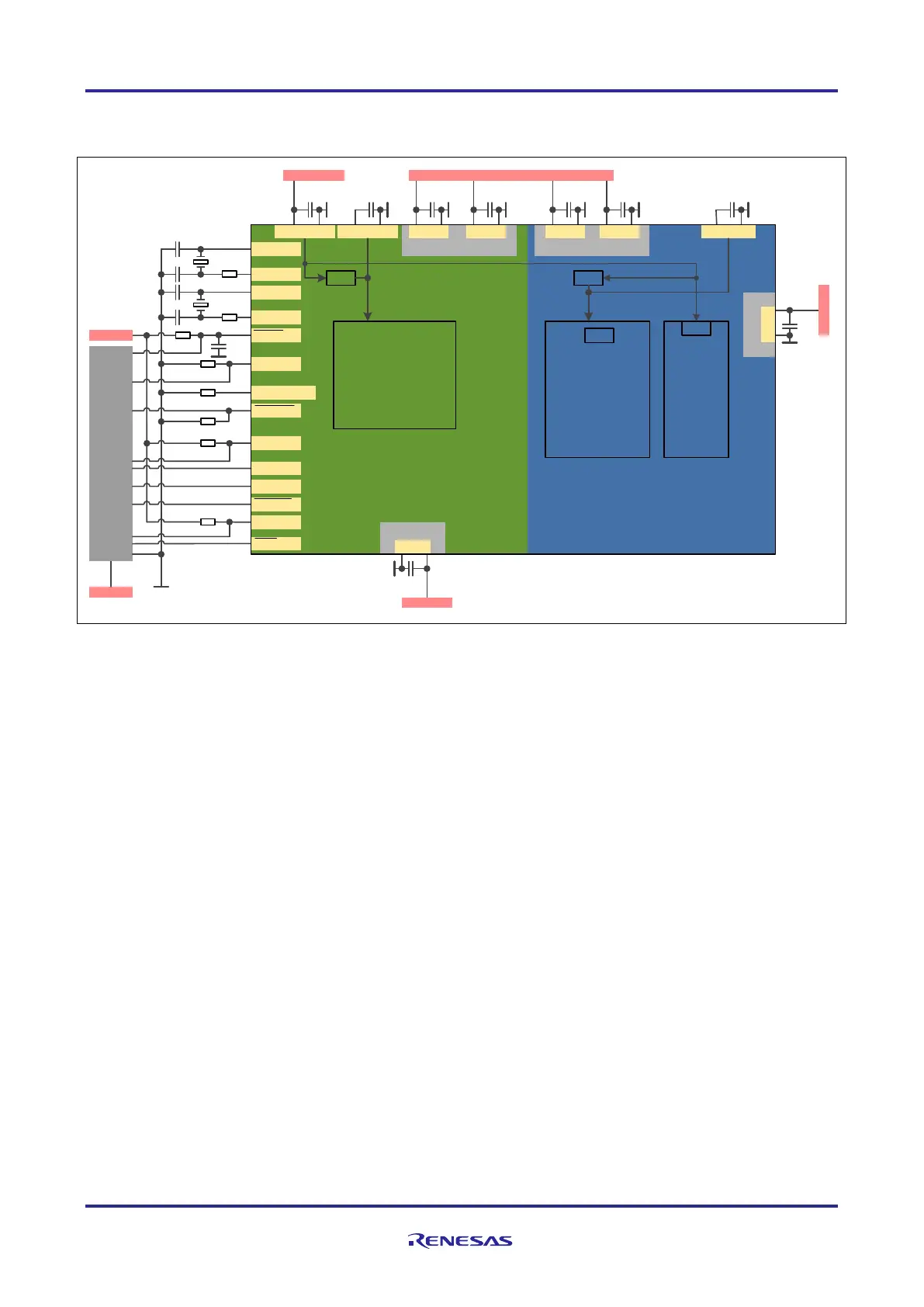

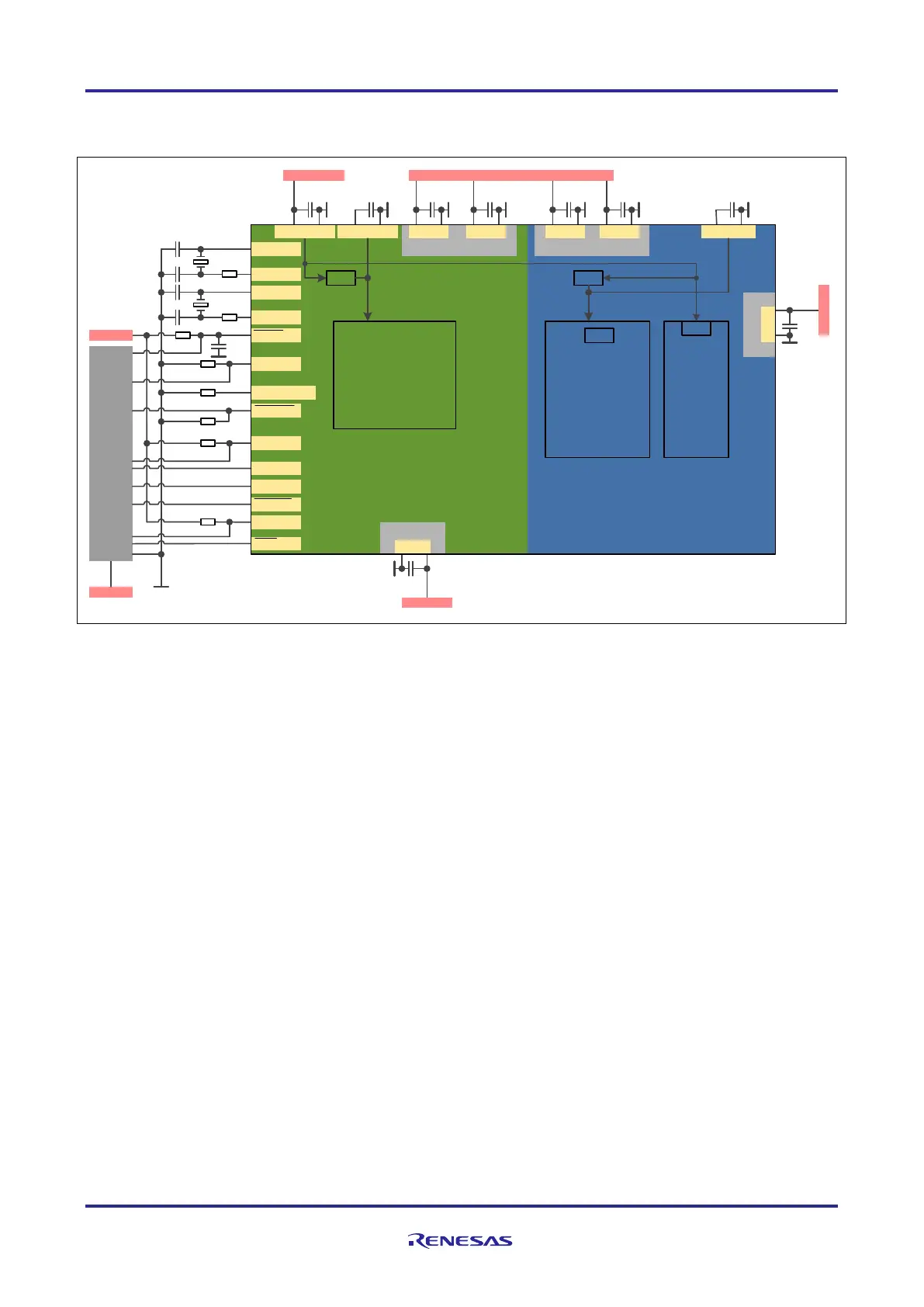

2.5 Minimum External Components of RH850/F1K

Figure 25: Minimum external components of RH850/F1K in normal operating mode

Note: The debug interface connections shown covers Nexus, LPD (1 pin) and LPD (4 pins). For details of the single

debug connection, see Chapter 8, Development Tool Interface for the corresponding debug interface. For details

of other external components, see their related chapters.

ADCA1

AD1

Port

EVCC ISOVCL

Port

EVCCAWOVCL

ADCA0

AD0

A0VREF

C6

C9

A1VREF

C12C13 C10C15

X1

X2

IP0_0

XT1

RESET

FLMD0

P10_8/FLMD1

DCUT R ST

DCUTDI

DCUTDO

DCUC LK

DCURDY

DCUTMS

EVCC

C14

EVCC

Debu g

VDD

REG

Logic

Logic Flash

REG

REG

C1

Q1

Q2

C2

C3

C4

R1

R2

R3

R4

R5

Cor e

C5

R6

EVTO

EVCC

R7

R8

EVCC

C11

REG VCC

REG VCC

C16

Loading...

Loading...