RH850/F1Kx, RH850/F1K Series Hardware Design Guide

R01AN3841ED0110 Rev. 1.10 Page 87 of 108

August 8, 2019

6. AD-Converter

6.1 Conversion time

The ADC conversion time consists of a number of timing parameters, which are summed-up to get the conversion

timing depending on the application.

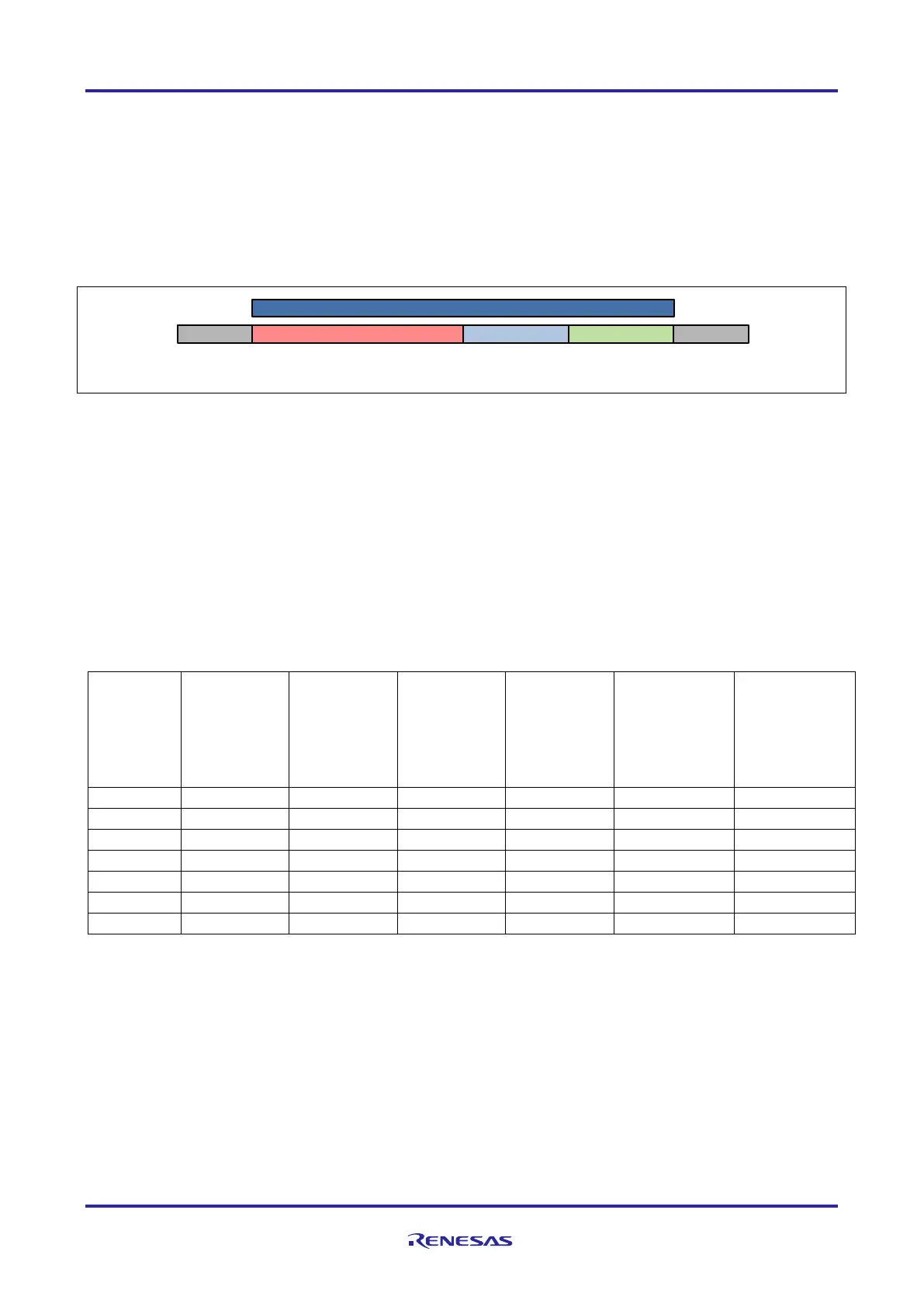

Figure 33: ADC conversion time

The setting of the ADC clock and the sampling time results in the following conversion timing:

Table 66: ADC conversion time overview

[MHz]

time

[clks]

time

[µs]

time

[µs]

time

[µs]

conversion

time

(excluding

MPX)

conversion

time

(including

MPX)

Note: The sampling time is set by the ADCAnSMPCR.SMPT [7:0] bits.

SG setup MPX setup Sampling Conversion

SG end

Total conversion time (single channel)

4c lks HWTRG

9clks SWTRG

Sampling clock + conversion clocks 18cl ks or 24cl ks 6clks22cl ks

Loading...

Loading...